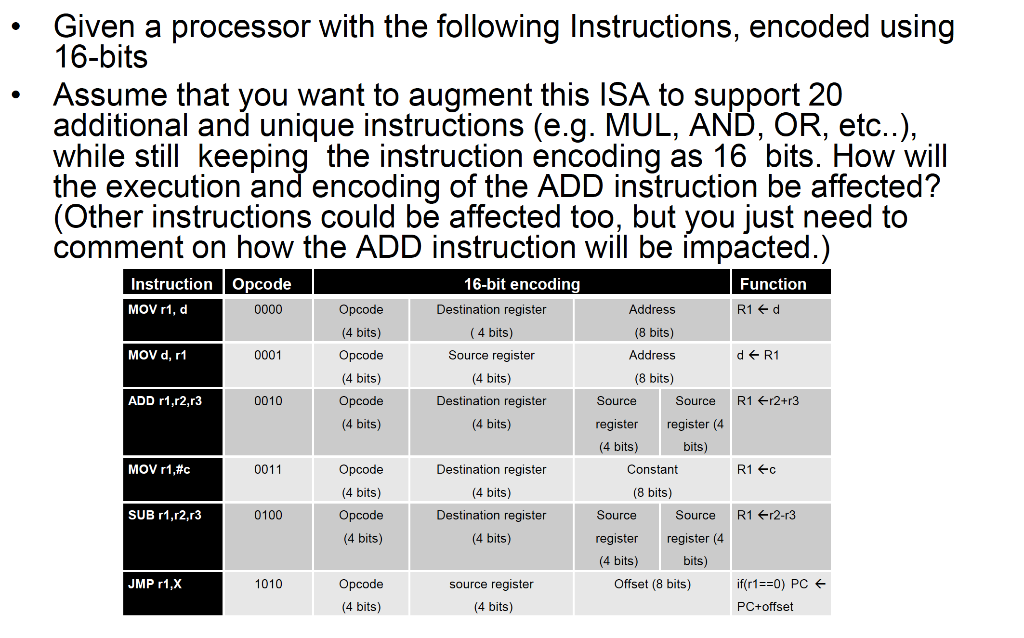

Question: Given a processor with the following Instructions, encoded using 16-bits Assume that you want to augment this ISA to support 20 additional and unique instructions

Given a processor with the following Instructions, encoded using 16-bits Assume that you want to augment this ISA to support 20 additional and unique instructions (e.g. MUL, AND, OR, etc..), while still keeping the instruction encoding as 16 bits. How will the execution and encoding of the ADD instruction be affected? (Other instructions could be affected too, but you just need to comment on how the ADD instruction will be mpcted.) Function R1d 16-bit encoding InstructionOpcode MOV r1, d Opcode (4 bits) Opcode (4 bits) Opcode (4 bits) Destination register (4 bits) Source register (4 bits) Destination register (4 bits) Address (8 bits) Address (8 bits) MOV d, r1 0001 Source R1 -r2+r3 Source register (4 bits) ADD r1,r2,r3 0010 register (4 bits) Constant Opcode (4 bits) Opcode 4 bits) Destination register (4 bits) Destination register (4 bits) MOV r1,#c 0011 (8 bits) Source R1 r2-r3 Source register (4 bits) SUB r1,r2,r3 0100 register (4 bits) Offset (8 bits) source register (4 bits) 1010 Opcode 4 bits) JMP r1,X PC+offset Given a processor with the following Instructions, encoded using 16-bits Assume that you want to augment this ISA to support 20 additional and unique instructions (e.g. MUL, AND, OR, etc..), while still keeping the instruction encoding as 16 bits. How will the execution and encoding of the ADD instruction be affected? (Other instructions could be affected too, but you just need to comment on how the ADD instruction will be mpcted.) Function R1d 16-bit encoding InstructionOpcode MOV r1, d Opcode (4 bits) Opcode (4 bits) Opcode (4 bits) Destination register (4 bits) Source register (4 bits) Destination register (4 bits) Address (8 bits) Address (8 bits) MOV d, r1 0001 Source R1 -r2+r3 Source register (4 bits) ADD r1,r2,r3 0010 register (4 bits) Constant Opcode (4 bits) Opcode 4 bits) Destination register (4 bits) Destination register (4 bits) MOV r1,#c 0011 (8 bits) Source R1 r2-r3 Source register (4 bits) SUB r1,r2,r3 0100 register (4 bits) Offset (8 bits) source register (4 bits) 1010 Opcode 4 bits) JMP r1,X PC+offset

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts