Question: Given a single-cycle datapath processor with a single stuck-at-1 fault at the ALUsrc control signal i.e. regardless of what it should be, the signal is

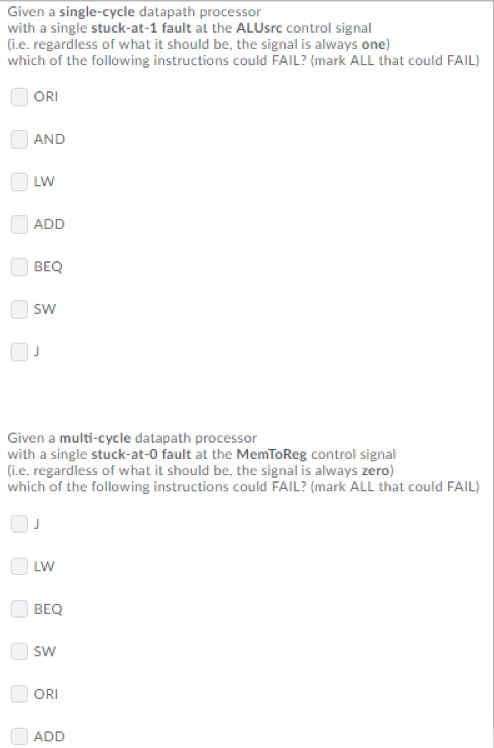

Given a single-cycle datapath processor with a single stuck-at-1 fault at the ALUsrc control signal i.e. regardless of what it should be, the signal is always one) which of the following instructions could FAIL? (mark ALL that could FAIL) ORI AND LW ADD BEQ SW Given a multi-cycle datapath processor with a single stuck-at-0 fault at the MemToReg control signal (i.e. regardless of what it should be, the signal is always zero) which of the following instructions could FAIL? (mark ALL that could FAIL) LW BEQ SW ORI ADD Given a single-cycle datapath processor with a single stuck-at-1 fault at the ALUsrc control signal i.e. regardless of what it should be, the signal is always one) which of the following instructions could FAIL? (mark ALL that could FAIL) ORI AND LW ADD BEQ SW Given a multi-cycle datapath processor with a single stuck-at-0 fault at the MemToReg control signal (i.e. regardless of what it should be, the signal is always zero) which of the following instructions could FAIL? (mark ALL that could FAIL) LW BEQ SW ORI ADD

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts