Question: Given a static multiple issue unit for the MIPS processor where the system can do a arithmetic/branch instruction with one issue slot and a load/store

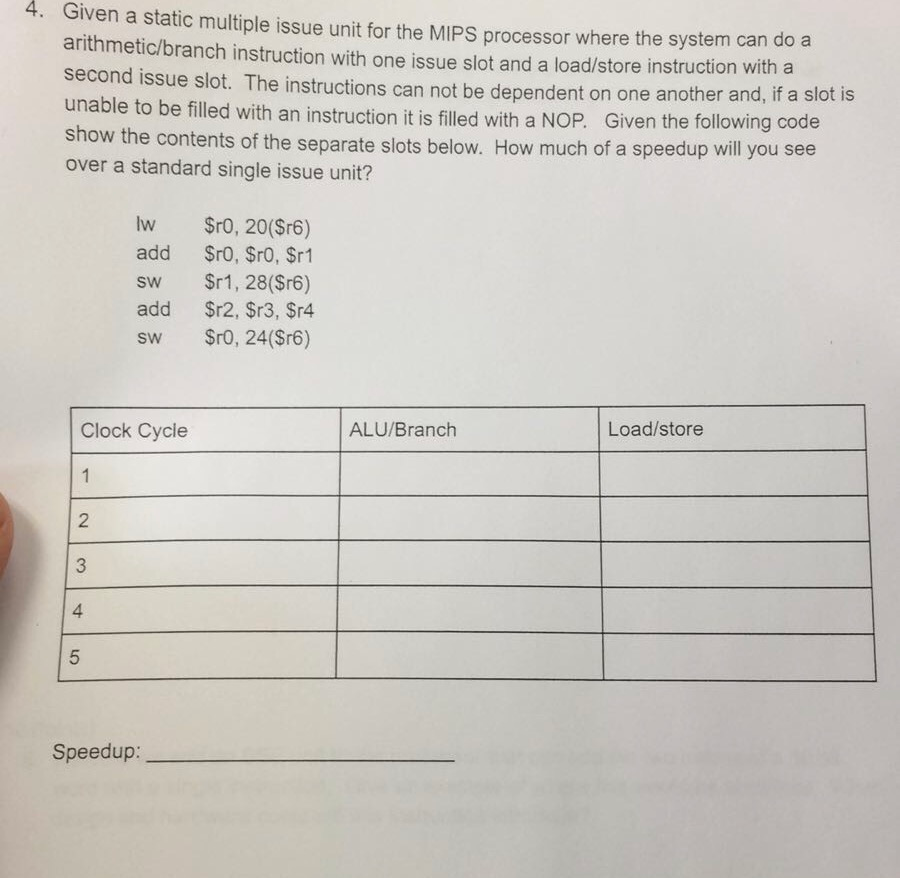

Given a static multiple issue unit for the MIPS processor where the system can do a arithmetic/branch instruction with one issue slot and a load/store instruction with a second issue slot. The instructions can not be dependent on one another and, if a slot is unable to be filled with an instruction it is filled with a NOP. Given the following code show the contents of the separate slot below. How much of a speedup will you see over a standard single issue unit? lw $r0, 20($r6) add $r0, $r0, $r1 sw $r1, 28($r6) add $r2, $r3, $r4 sw $r0, 24($r6) Speedup: _____

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts