Question: Given the following Full Adder circuit: a) Define a UDP that implements 3-input majority gate (Maj). Assume that the inputs will never take the value

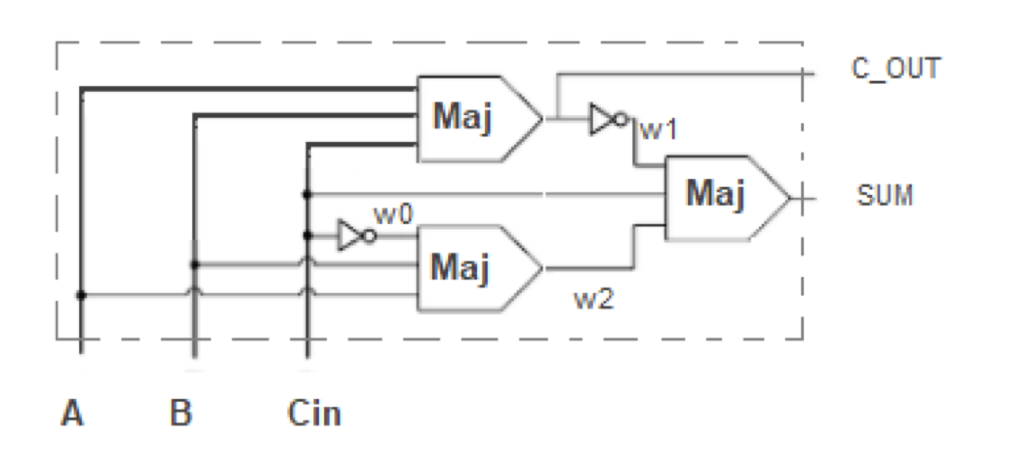

Given the following Full Adder circuit:

a) Define a UDP that implements 3-input majority gate (Maj). Assume that the inputs will never take the value x.

b) Create a Full adder module that uses the UDP designed in (a). Then create a test bench to obtain outputs and waveforms.

C OUT Ma w1 Maj SUM Majw2 A B Cin C OUT Ma w1 Maj SUM Majw2 A B Cin

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts