Question: Given the following MIPS sequence: Assume that the sequence is executed by a 5-stage pipelined MIPS processor a) Draw a multi-cycle pipeline diagram for the

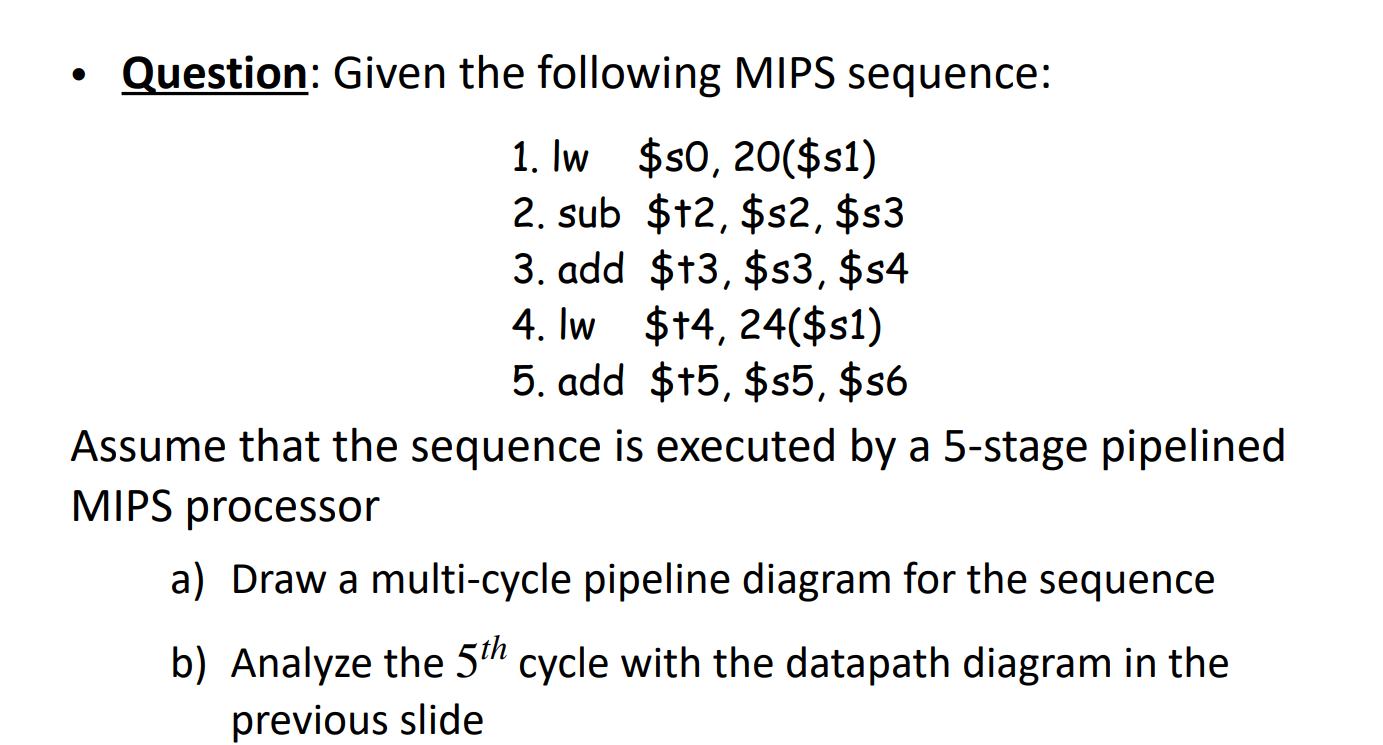

Given the following MIPS sequence: Assume that the sequence is executed by a 5-stage pipelined MIPS processor a) Draw a multi-cycle pipeline diagram for the sequence b) Analyze the cycle with the datapath diagram in the previous slide 5th 35 1. lw $s0, 20($s1) 2. sub $t2, $s2, $s3 3. add $t3, $s3, $s4 4. lw $t4, 24($s1) 5. add $t5, $s5, $s6

Given the following MIPS sequence: Assume that the sequence is executed by a 5-stage pipelined MIPS processor a) Draw a multi-cycle pipeline diagram for the sequence b) Analyze the cycle with the datapath diagram in the previous slide 5th 35 1. lw $s0, 20($s1) 2. sub $t2, $s2, $s3 3. add $t3, $s3, $s4 4. lw $t4, 24($s1) 5. add $t5, $s5, $s6

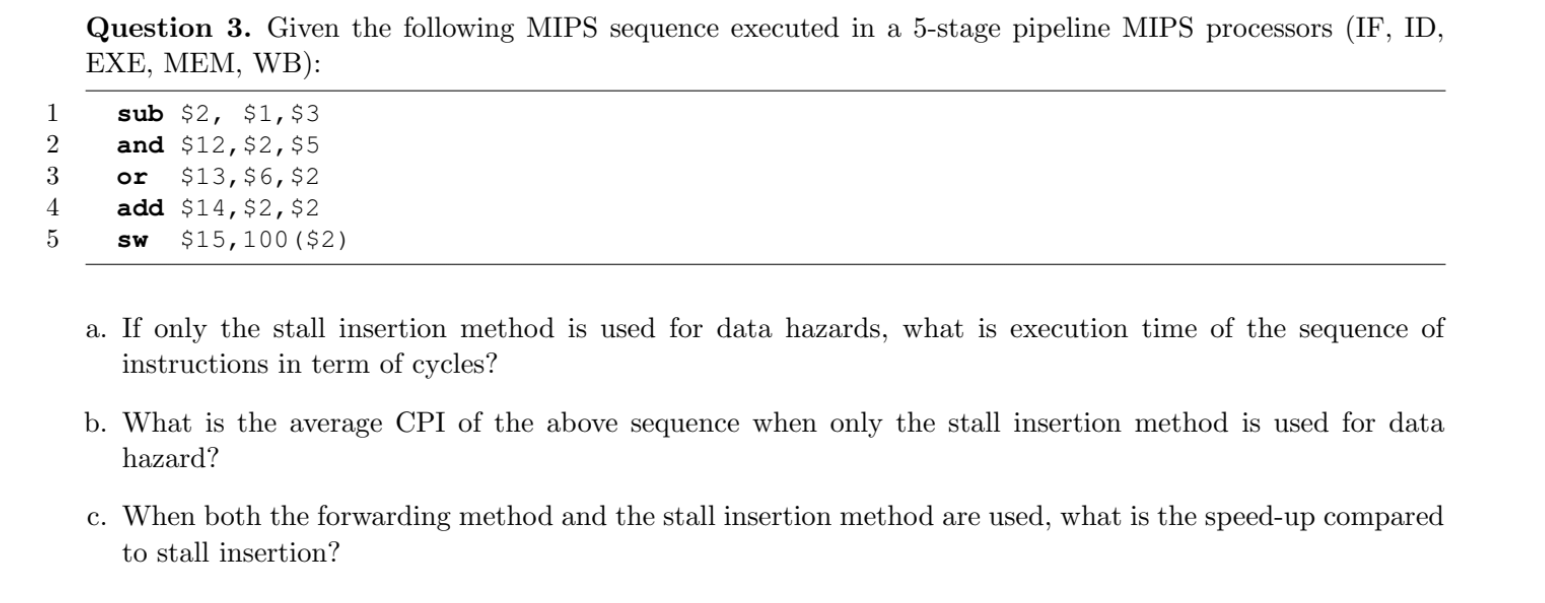

Question 3. Given the following MIPS sequence executed in a 5-stage pipeline MIPS processors (IF, ID, EXE, MEM, WB): sub$2,$1,$3and$12,$2,$5or$13,$6,$2add$14,$2,$2sw$15,100($2) a. If only the stall insertion method is used for data hazards, what is execution time of the sequence of instructions in term of cycles? b. What is the average CPI of the above sequence when only the stall insertion method is used for data hazard? c. When both the forwarding method and the stall insertion method are used, what is the speed-up compared to stall insertion? - Question: Given the following MIPS sequence: 1. Iw \$so, 20(\$s1) 2. sub $+2,$s2,$s3 3. add $+3,$s3,$s4 4. Iw $+4,24($s1) 5. add $+5,$s5,$s6 Assume that the sequence is executed by a 5-stage pipelined MIPS processor a) Draw a multi-cycle pipeline diagram for the sequence b) Analyze the 5th cycle with the datapath diagram in the previous slide

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts