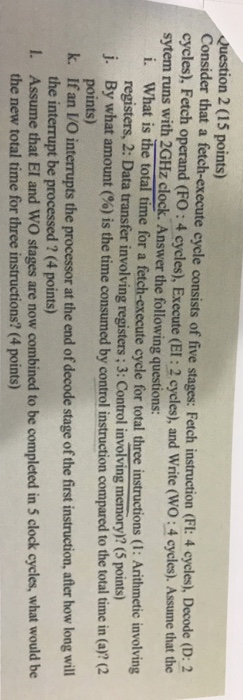

Question: Help duestion 2 (15 points) Consider that a fetch-execute cycle consists of five stages: Fetch instruction (FI: 4 cycles), Decode (D: 2 cycles), Fetch operand

duestion 2 (15 points) Consider that a fetch-execute cycle consists of five stages: Fetch instruction (FI: 4 cycles), Decode (D: 2 cycles), Fetch operand (FO:4 cycles), Execute (EI: 2 cycles), and Write (WO :4 cycles). Assume that the sytem runs with 2GHz clock. Answer the following questions i. What is the total time for a fetch-execute cycle for total three instructions (I: Arithmetic involving registers, 2: Data transfer involving registers; 3: Control involving memory)? (5 points) By what amount (%) is the time consumed by control instruction compared to the total time in (a)? (2 points) j. k. If an V/O interrupts the processor at the end of decode stage of the first instruction, after how long will L. Assume that El and WO stages are now combined to be completed in 5 clock cycles, what would be the interrupt be processed ? (4 points) the new total time for three instructions? (4 points)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts