Question: I actually need the answer for ONLY QUESTION 5. But I uploaded question 4 as well because you may require question 4 to solve question

I actually need the answer for ONLY QUESTION 5. But I uploaded question 4 as well because you may require question 4 to solve question 5.

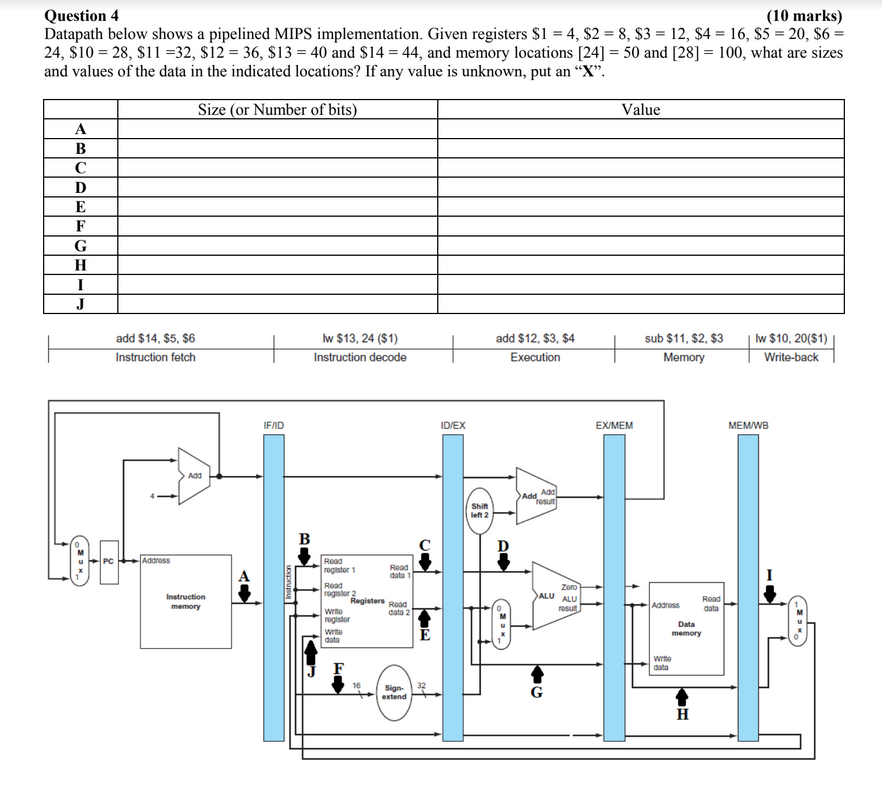

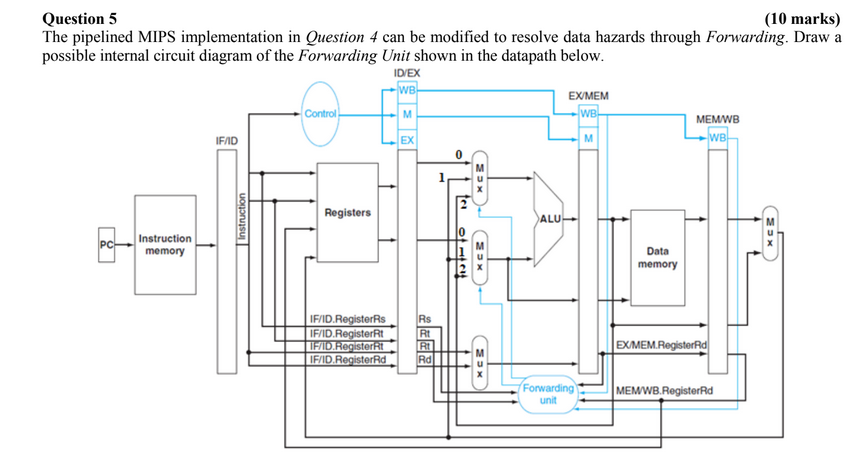

Question 4 (10 marks) Datapath below shows a pipelined MIPS implementation. Given registers $1 = 4, $2 = 8, $3 = 12, $4 = 16, $5 = 20, $6 = 24, $10 = 28, $11 =32, $12 = 36, $13 = 40 and $14 = 44, and memory locations [24] = 50 and [28] = 100, what are sizes and values of the data in the indicated locations? If any value is unknown, put an X. Size (or Number of bits) Value A B D E F G H I J add $14. $5, $6 Instruction fetch lw $13, 24 (51) Instruction decode add $12, $3, $4 Execution sub $11, $2. $3 Memory lw $10, 20($1) Write-back IFAD ID/EX EX/MEM MEM/WB Add Add 400 Tosuit Shift left 2 B D PC Address Road data 1 Zoro Road register 1 Read register 2 Write register Write data Instruction memory ALU ALU Registers Rood data 2 OSUR Road Address data Data memory E Writte data 16 Sign- extend H Question 5 (10 marks) The pipelined MIPS implementation in Question 4 can be modified to resolve data hazards through Forwarding. Draw a possible internal circuit diagram of the Forwarding Unit shown in the datapath below. IDEX WB EX/MEM Control M WB MEMWB IF/ID M EX WB 1 Instruction Registers ALU PC Instruction memory Data memory IF/ID. Registers IF/ID. Register IF/ID. Register IF/ID. RegisterRd Rs Rt RI Rd EXMEM. Registered Forwarding unit MEMWB. RegisterRd Question 4 (10 marks) Datapath below shows a pipelined MIPS implementation. Given registers $1 = 4, $2 = 8, $3 = 12, $4 = 16, $5 = 20, $6 = 24, $10 = 28, $11 =32, $12 = 36, $13 = 40 and $14 = 44, and memory locations [24] = 50 and [28] = 100, what are sizes and values of the data in the indicated locations? If any value is unknown, put an X. Size (or Number of bits) Value A B D E F G H I J add $14. $5, $6 Instruction fetch lw $13, 24 (51) Instruction decode add $12, $3, $4 Execution sub $11, $2. $3 Memory lw $10, 20($1) Write-back IFAD ID/EX EX/MEM MEM/WB Add Add 400 Tosuit Shift left 2 B D PC Address Road data 1 Zoro Road register 1 Read register 2 Write register Write data Instruction memory ALU ALU Registers Rood data 2 OSUR Road Address data Data memory E Writte data 16 Sign- extend H Question 5 (10 marks) The pipelined MIPS implementation in Question 4 can be modified to resolve data hazards through Forwarding. Draw a possible internal circuit diagram of the Forwarding Unit shown in the datapath below. IDEX WB EX/MEM Control M WB MEMWB IF/ID M EX WB 1 Instruction Registers ALU PC Instruction memory Data memory IF/ID. Registers IF/ID. Register IF/ID. Register IF/ID. RegisterRd Rs Rt RI Rd EXMEM. Registered Forwarding unit MEMWB. RegisterRd

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts