Question: I have designed this counter in Verlilog code using ModelSim, but the output of the counter doesn't work, and I don't know why. Can anyone

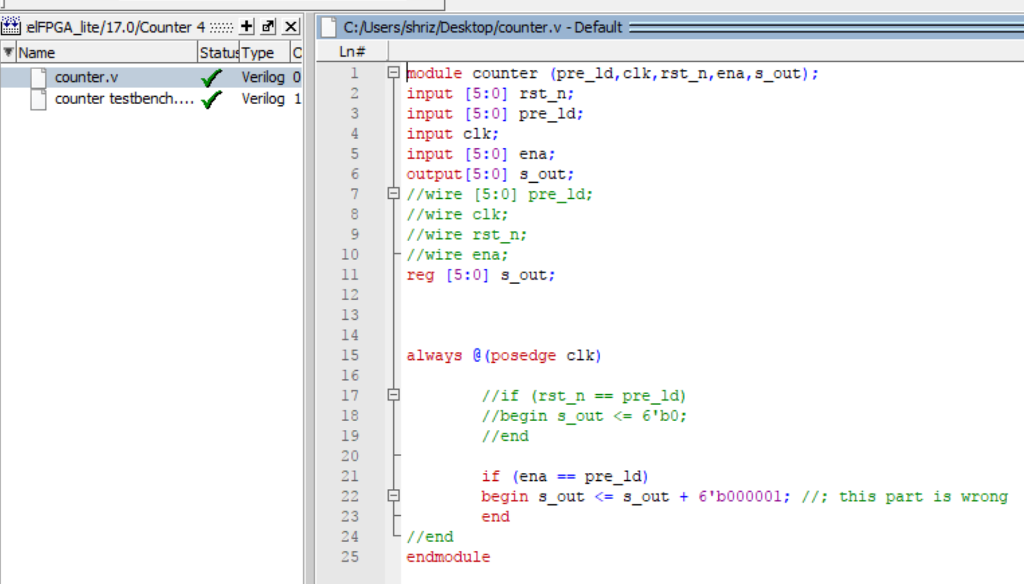

I have designed this counter in Verlilog code using ModelSim, but the output of the counter doesn't work, and I don't know why. Can anyone help me fix the code so the code works properly?

This is my assignement:

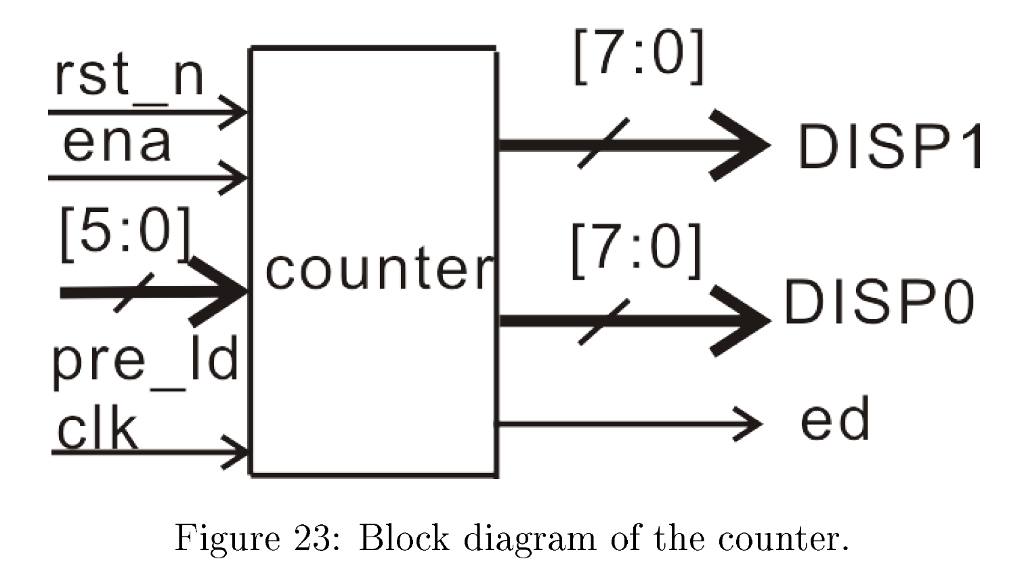

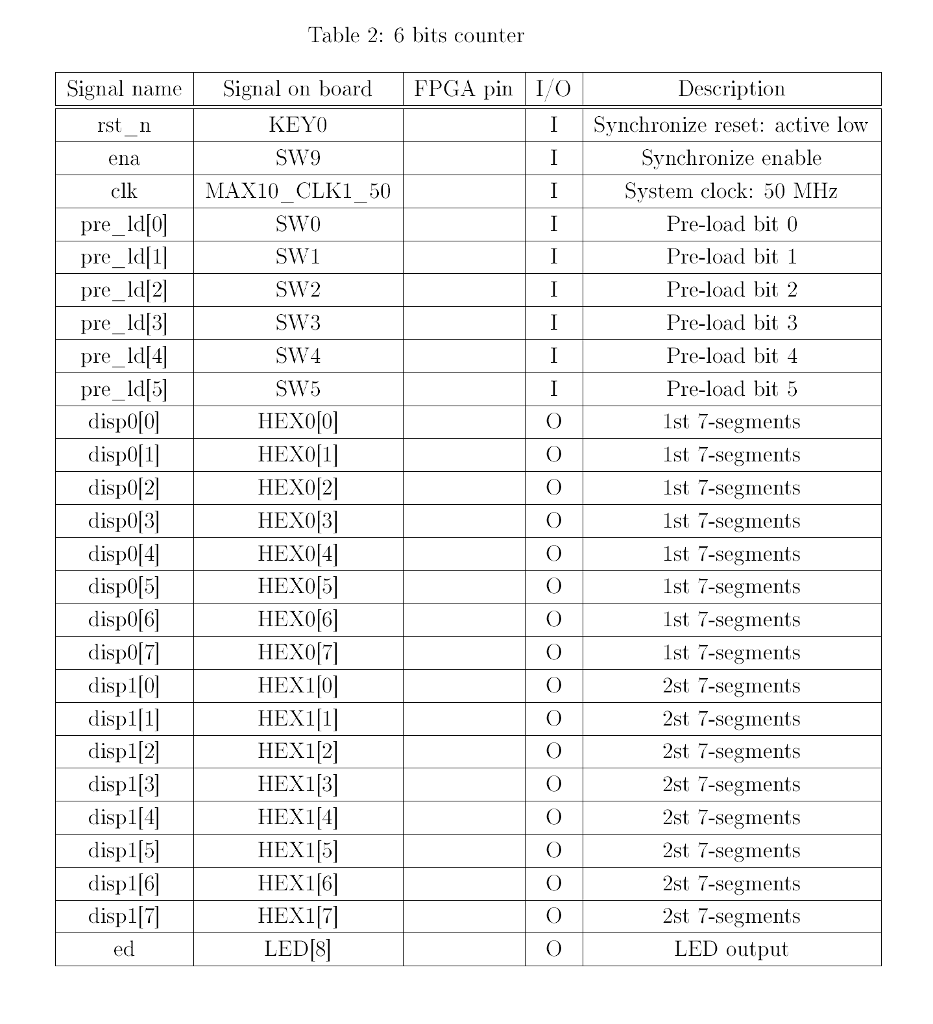

Counter In sequential circuits, counter is one of most widely used function blocks. They may be utilized to count the number of occurrences of the events, generate control signal at the certain time, and so on. Specifcation In this lab, a pre-load increment counter is required to be designed and tested based upon DE10-Lite FPGA board. A counter can be implemented by using if else or a FSM. The specications of the counter are listed as below: Synchronized reset. The counter is activated by an enable signal 6 bits pre-load value set by 6 switches to determine the termination condition of the counter. End-flag signal reected through a LED. Pre-load value converted to the decimal number is mapped to 7- segments display.

Pre_ld= 110101

and complete this Table.

I am mostly done, my my code isn't working properly, please help me fix it.

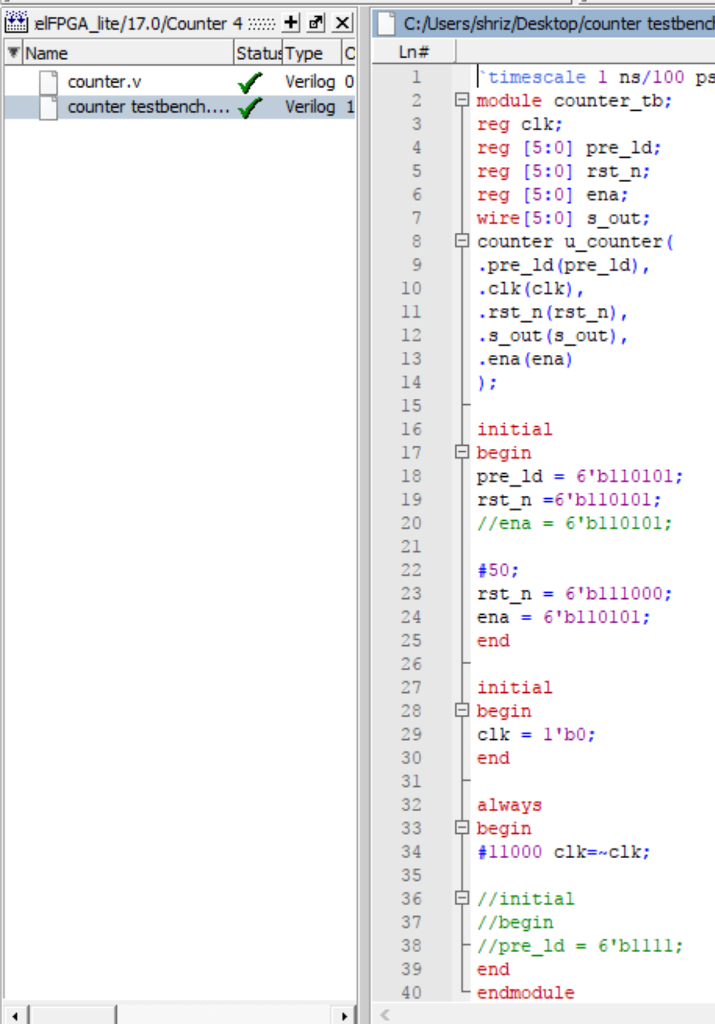

this is my Testbench file:

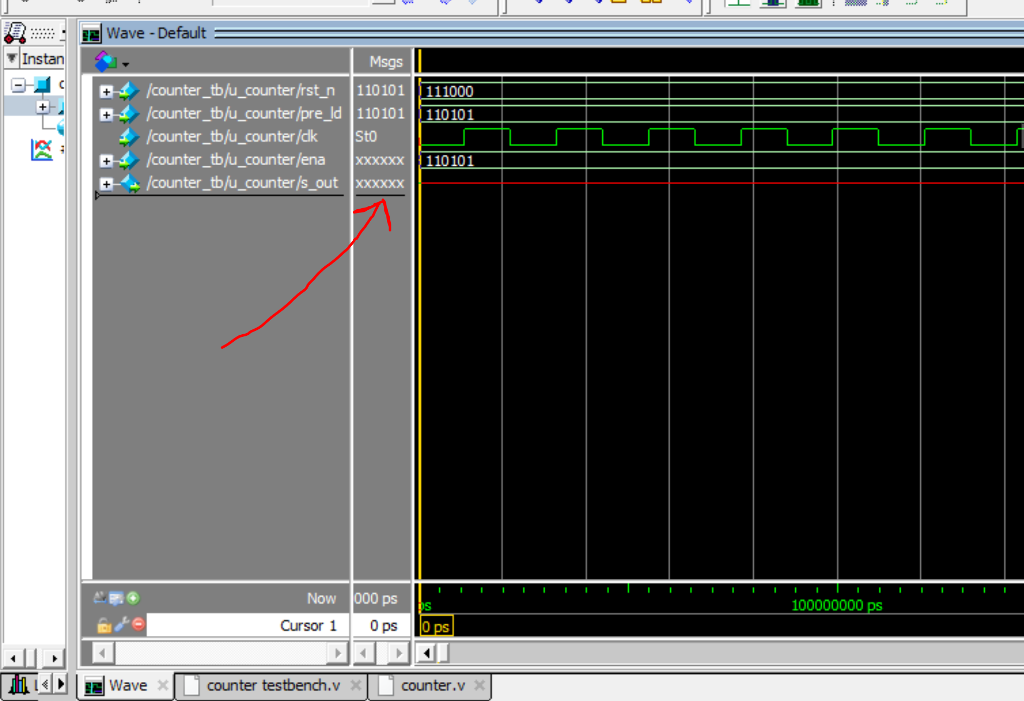

and this is the waveform:

rst n [7:0] DISP1 ena [5:0] pre_ld |counter! [70] DISPO ed Figure 23: Block diagram of the counter

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts