Question: I have trouble with my VHDL code, it is supposed to find the 2's complement of an 8 bit input using a Moore style FSM

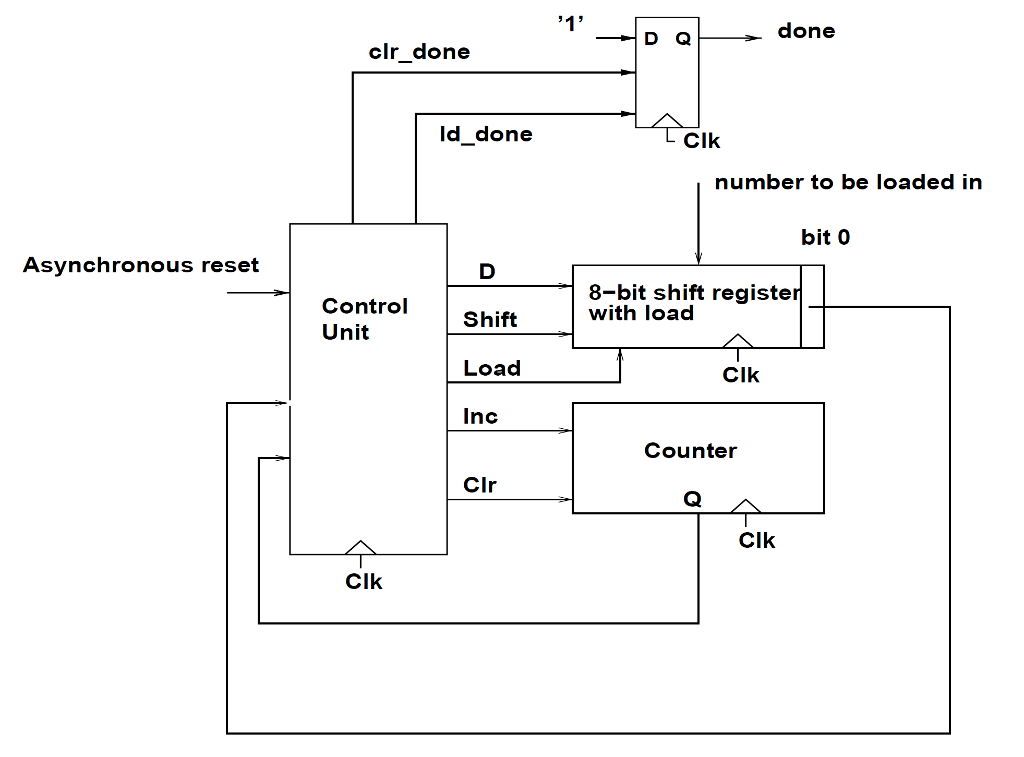

I have trouble with my VHDL code, it is supposed to find the 2's complement of an 8 bit input using a Moore style FSM to implement the control unit. The algorithm begins by first loading a number into the 8-bit shift register and clearing the counter and done flipflop to 0. The least significant bit of the shift register is examined, and based upon its value the control unit then sets the D signal to the appropriate value and shifts it into the most significant position of the shift register. This process is repeated until all 8 bits of the original number have been examined. At this point, the shift register will contain the twos complement of the original number. A Done flip-flop is used to indicate that the algorithm is complete. I would appreciate the help.

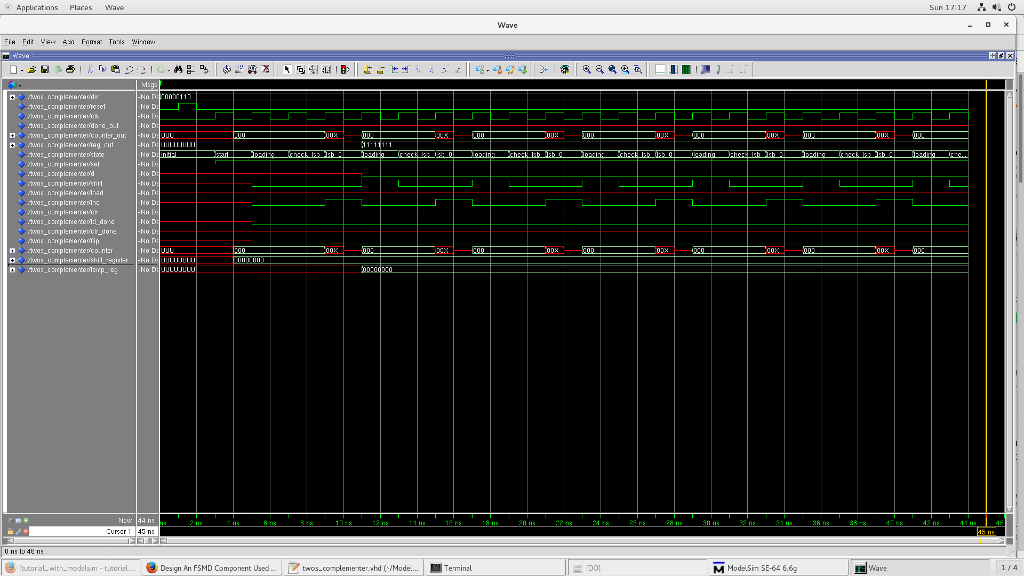

This is what I have so far but there is some issues with the outputs:

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; use IEEE.numeric_std.all; entity twos_complementer is port(din : in std_logic_vector(7 downto 0); reset : in std_logic ; clk : in std_logic ; done_out : out std_logic ; counter_out : out std_logic_vector(2 downto 0); reg_out : out std_logic_vector(7 downto 0)); end twos_complementer ; architecture twos_complementer_behav of twos_complementer is --states type state_type is (initial, start, loading, check_lsb, check_flip, lsb_0, lsb_1, invert, finish); signal state : state_type; --signals signal set, d, shift, load, inc, clr, ld_done, clr_done, flip : std_logic; signal counter : std_logic_vector(2 downto 0); signal shift_register, temp_reg : std_logic_vector(7 downto 0); begin process(reset, clk, counter, shift_register) --control unit begin if (reset = '1') then --reset counter set --initialize signals load shift inc inc d d d ld_done -- end case; else --nothing end if; end process; process (clk, inc, clr) --counter begin --reset if (set = '1') then counter clr done ld_done Clk number to be loaded in bit 0 Asynchronous reset Control Shift Unit 8-bit shift registe with load Load Inc Counter CIr Clk

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts