Question: I need help with the following Computer Architecture problem: 3. Suppose we have the following latencies for various datapath units. Latency in ps 200 50

I need help with the following Computer Architecture problem:

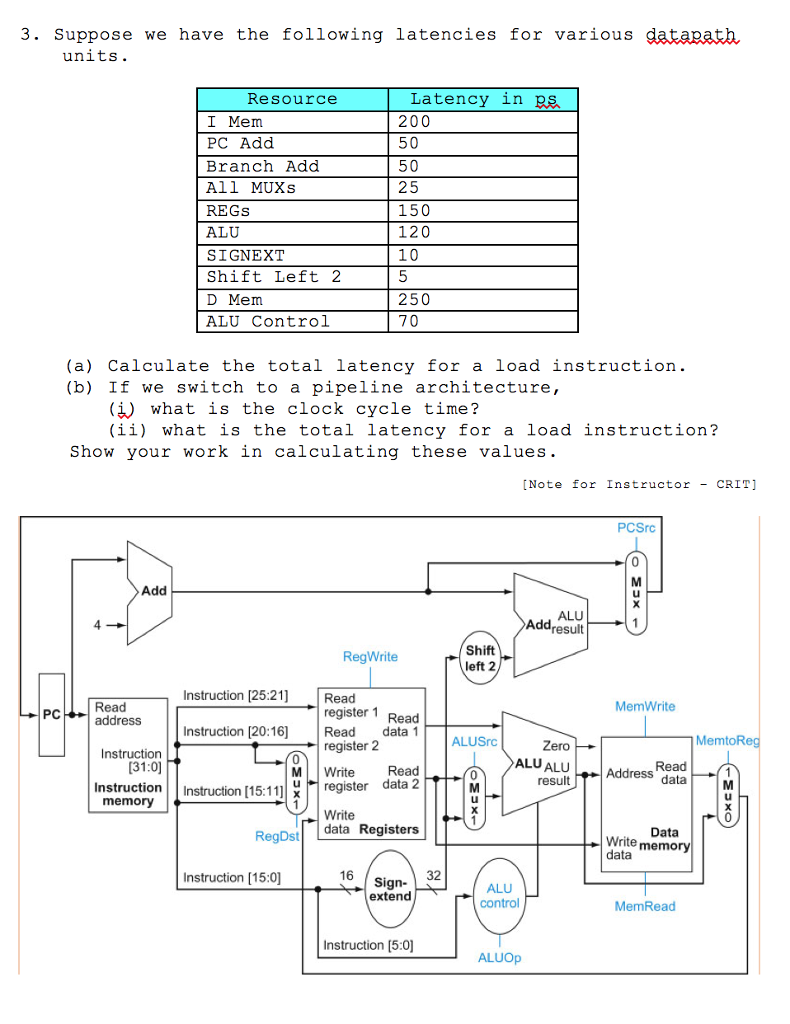

3. Suppose we have the following latencies for various datapath units. Latency in ps 200 50 50 25 150 120 10 Resource I Mem PC Add Branch Add All MUXs REGs ALU SIGNEXT Shift Left 2 D Menm ALU Control 250 70 (a) Calculate the total latency for a load instruction. (b) If we switch to a pipeline architecture, what is the clock cycle time ? (ii) what is the total latency for a load instruction? Show your work ln calculating these values. [Note for InstructorCRIT] PCSrc Add ALU Addresult 4 Shift left 2 RegWrite Instruction [25:21 Read Read MemWrite register 1 Read Instruction [20:16 Read data1 M Write Read register data 2 data Registers PCaddress ALUSrc MemtoR register 2 Instruction ALU ALU result Read Address dataM (31:0 Instruction | | Instruction [15:11] memory Write 0 RegDst Write memory Data Instruction [15:0] 16 32 Sign- extend ALU MemRead Instruction [5:0] ALUOp

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts