Question: I really need help with the code itself. Using Verilog gate-level behavioral specification, construct a simulation of the programmable ALU, whose schematic is shown below.

I really need help with the code itself.

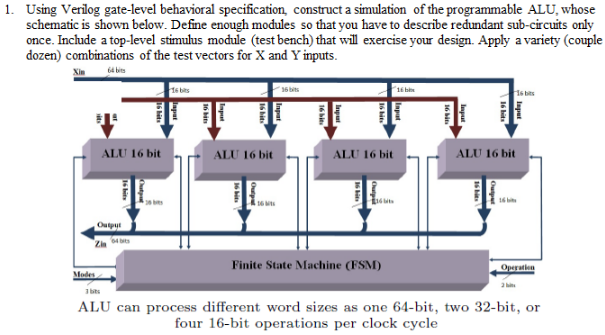

Using Verilog gate-level behavioral specification, construct a simulation of the programmable ALU, whose schematic is shown below. Define enough modules so that you have to describe redundant sub-circuits only once. Inchude a top-level stimulus module (test bench) that will exercise your design. Apply a variety (couple dozen) combinations of the test vectors for X and Yinputs 1. Xin 64 bits ALU 16 bit ALU 16 bit ALU 16 bit ALU 16 bit Output Finite State Machine (FSM) ALU can process different word sizes as one 64-bit, two 32-bit, or four 16-bit operations per clock cycle

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts