Question: Using Verilog gate-level behavioral specification, construct a simulation of the programmable ALU, whose schematic is shown below. Define enough modules so that you have.to describe

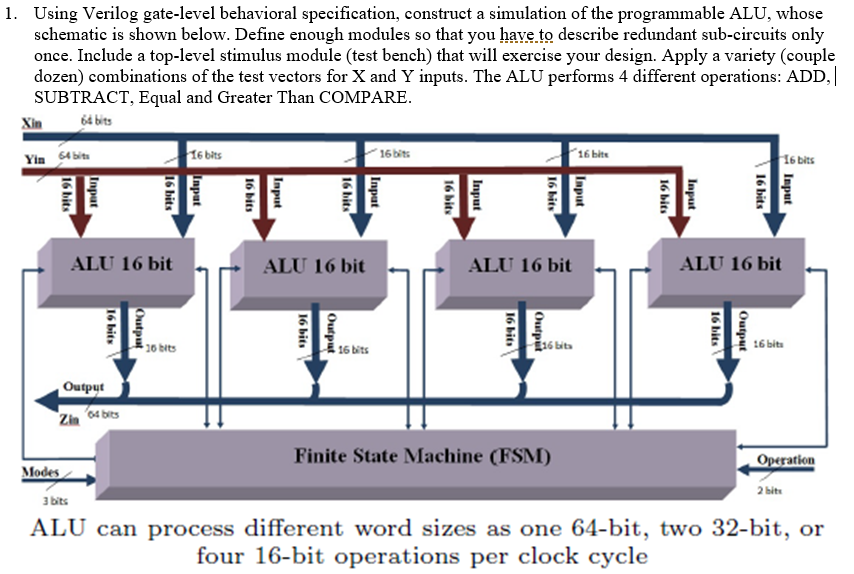

Using Verilog gate-level behavioral specification, construct a simulation of the programmable ALU, whose schematic is shown below. Define enough modules so that you have.to describe redundant sub-circuits only once. Include a top-level stimulus module (test bench) that will exercise your design. Apply a variety (couple dozen) combinations of the test vectors for X and Y inputs. The ALU performs 4 different operations: ADD,| SUBTRACT, Equal and Greater Than COMPARE 1. Xin64 Yin 4bit 16 bits 16bi 16 bite 6 bits ALU 16 bit ALU 16 bit ALU 16 bit ALU 16 bit 7 6 bits E.16 bit n26 bita 6 bits Output Zin 04bt Finite State Machine (FSM) Modes 2 bits 3 bits ALU can process different word sizes as one 64-bit, two 32-bit, or four 16-bit operations per clock cycle

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts