Question: ICT 114 Computer Architecture PLEASE PROVIDE WORKING AND FORMULA AND EXPLANATION Question 2 (25 marks) Figure Q2 shows the characteristics of a hypothetical machine, relevant

ICT 114 Computer Architecture

PLEASE PROVIDE WORKING AND FORMULA AND EXPLANATION

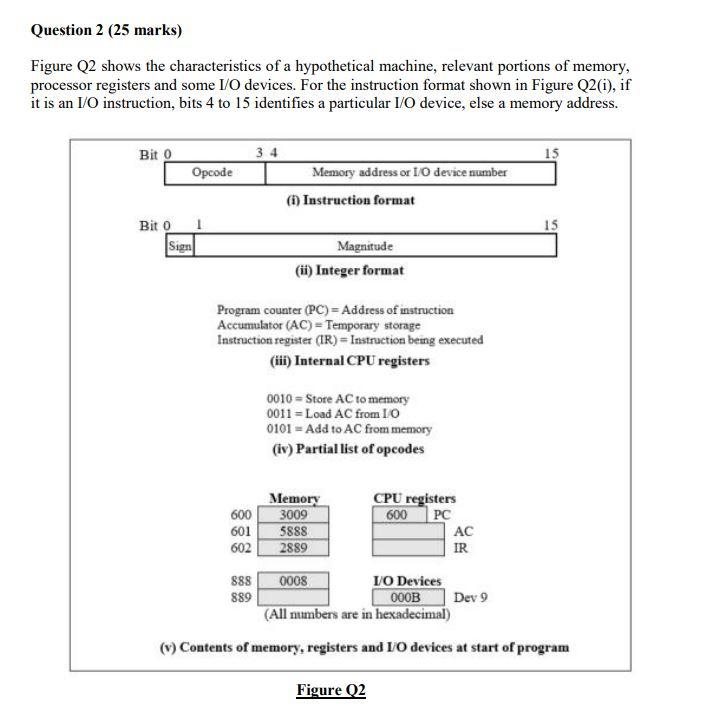

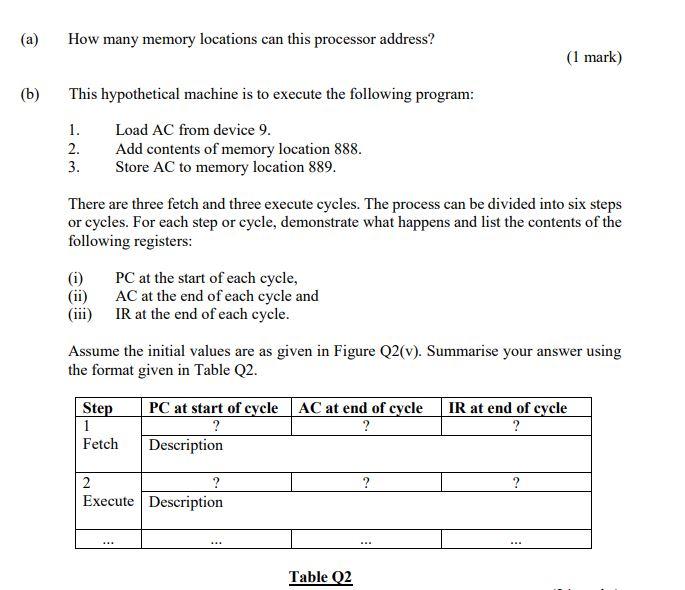

Question 2 (25 marks) Figure Q2 shows the characteristics of a hypothetical machine, relevant portions of memory, processor registers and some I/O devices. For the instruction format shown in Figure Q2(1), if it is an 1/0 instruction, bits 4 to 15 identifies a particular 1/0 device, else a memory address. Bit o 15 Opcode Memory address or 110 device number Instruction format 15 Bito 1 Sign Magnitude (ii) Integer format Program counter (PC)= Address of instruction Accumulator (AC) - Temporary storage Instruction register (IR)= Instruction being executed (iii) Internal CPU registers 0010 = Store AC to memory 0011 = Load AC from 10 0101 - Add to AC from memory (iv) Partial list of opcodes 600 601 602 Memory 3009 5888 2889 CPU registers 600 PC AC IR 888 0008 10 Devices 889 000B Dev 9 (All numbers are in hexadecimal) (m) Contents of memory, registers and 10 devices at start of program Figure Q2 (a) (b) How many memory locations can this processor address? (1 mark) This hypothetical machine is to execute the following program: 1. Load AC from device 9. 2. Add contents of memory location 888. 3. Store AC to memory location 889. There are three fetch and three execute cycles. The process can be divided into six steps or cycles. For each step or cycle, demonstrate what happens and list the contents of the following registers: (1) PC at the start of each cycle, (ii) AC at the end of each cycle and (iii) IR at the end of each cycle. Assume the initial values are as given in Figure Q2(V). Summarise your answer using the format given in Table Q2. Step 1 Fetch PC at start of cycle AC at end of cycle ? ? Description IR at end of cycle ? ? ? 2 ? Execute Description Table 02

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts