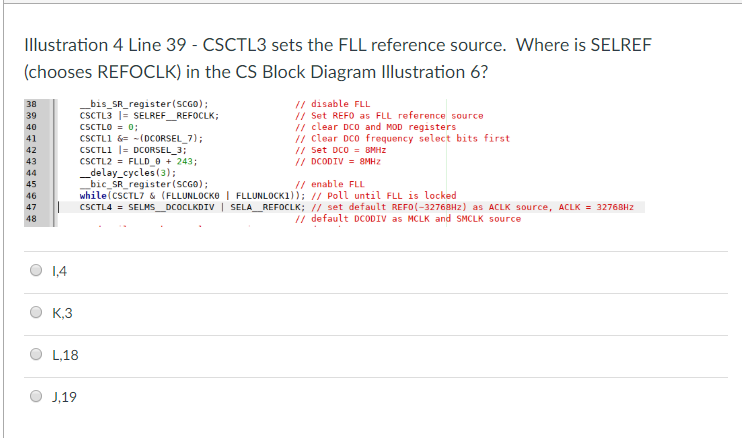

Question: Illustration 4 Line 39 - CSCTL3 sets the FLL reference source. Where is SELREF (chooses REFOCLK) in the CS Block Diagram Illustration 6? // disable

Illustration 4 Line 39 - CSCTL3 sets the FLL reference source. Where is SELREF (chooses REFOCLK) in the CS Block Diagram Illustration 6? // disable FLL 39 40 bis_SR_register(SCGO); CSCTL3 -SELREF REFOCLK; CSCTLO0; // Set REFO as FLL reference source clear DCo and MOD registers / Clear DCO frequency select bits first 42 43 CSCTLI 1-DCORSEL_3 CSCTL2 = FLLD-e + 243 ; // DCODIV = RMHz delay_cycles (3 -bic-SR-register(SCGO) ; while(cSCTL7&(FLLUNLOCKe I / enable FLL 45 46 47 Il FLLUNLOCKI) Poll until FLL is locked cscTL4 SELIIS DCOCLKDIV | SELA REFOCLK; // set default REF0(-32768Hz) as ACLK source, ACLK 32768Hz // default DCODIV as MCLK and SMCLK source 0 14 O K,3 O L18 J.19 Illustration 4 Line 39 - CSCTL3 sets the FLL reference source. Where is SELREF (chooses REFOCLK) in the CS Block Diagram Illustration 6? // disable FLL 39 40 bis_SR_register(SCGO); CSCTL3 -SELREF REFOCLK; CSCTLO0; // Set REFO as FLL reference source clear DCo and MOD registers / Clear DCO frequency select bits first 42 43 CSCTLI 1-DCORSEL_3 CSCTL2 = FLLD-e + 243 ; // DCODIV = RMHz delay_cycles (3 -bic-SR-register(SCGO) ; while(cSCTL7&(FLLUNLOCKe I / enable FLL 45 46 47 Il FLLUNLOCKI) Poll until FLL is locked cscTL4 SELIIS DCOCLKDIV | SELA REFOCLK; // set default REF0(-32768Hz) as ACLK source, ACLK 32768Hz // default DCODIV as MCLK and SMCLK source 0 14 O K,3 O L18 J.19

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts