Question: Im lost in my computer architecture class!!! Can someone help me out?!! It would help so much! thank you!!! PART 2 THAT IS REFERRED TO

Im lost in my computer architecture class!!! Can someone help me out?!! It would help so much! thank you!!!

PART 2 THAT IS REFERRED TO ABOVE!!!!!

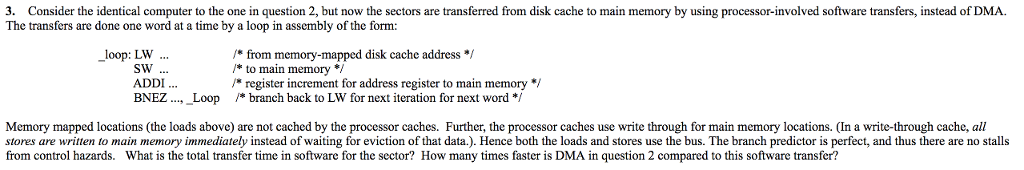

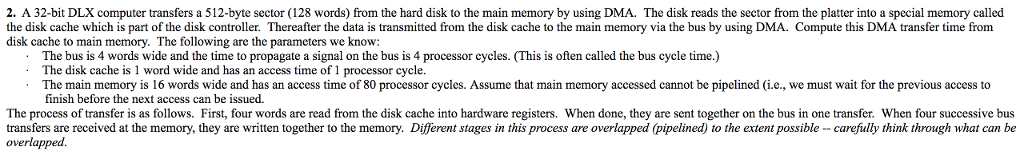

3. onsider the identical computer o he one in question ut now the sectors are transferre The transfers are done one word at a time by a loop in assembly of the form: rom is cac e to main memor b using processor inv i ed SOT war transe s nstead i M loop: LW. SW ADDI.. from memory-mapped disk cache address*/ * to main memory*, *register increment for address register to main memory */ Loop *branch back to LW for next iteration for next word* Memory mapped locations (the loads above) are not cached by the processor caches. Further, the processor caches use write through for main memory locations. (In a write-through cache, all stores are written to main memory immediately instead of waiting for eviction of that data.). Hence both the loads and stores use the bus. The branch predictor is perfect, and thus there are no stalls from control hazards. What is the total transfer time in software for the sector? How many times faster is DMA in question 2 compared to this software transfer? 3. onsider the identical computer o he one in question ut now the sectors are transferre The transfers are done one word at a time by a loop in assembly of the form: rom is cac e to main memor b using processor inv i ed SOT war transe s nstead i M loop: LW. SW ADDI.. from memory-mapped disk cache address*/ * to main memory*, *register increment for address register to main memory */ Loop *branch back to LW for next iteration for next word* Memory mapped locations (the loads above) are not cached by the processor caches. Further, the processor caches use write through for main memory locations. (In a write-through cache, all stores are written to main memory immediately instead of waiting for eviction of that data.). Hence both the loads and stores use the bus. The branch predictor is perfect, and thus there are no stalls from control hazards. What is the total transfer time in software for the sector? How many times faster is DMA in question 2 compared to this software transfer

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts