Question: in a 5 stage pipeline architecture, the following code is executed: lw $t1 , 0($t0) lw $t2 , 4($t0) add $t3 , $t2 , $t1

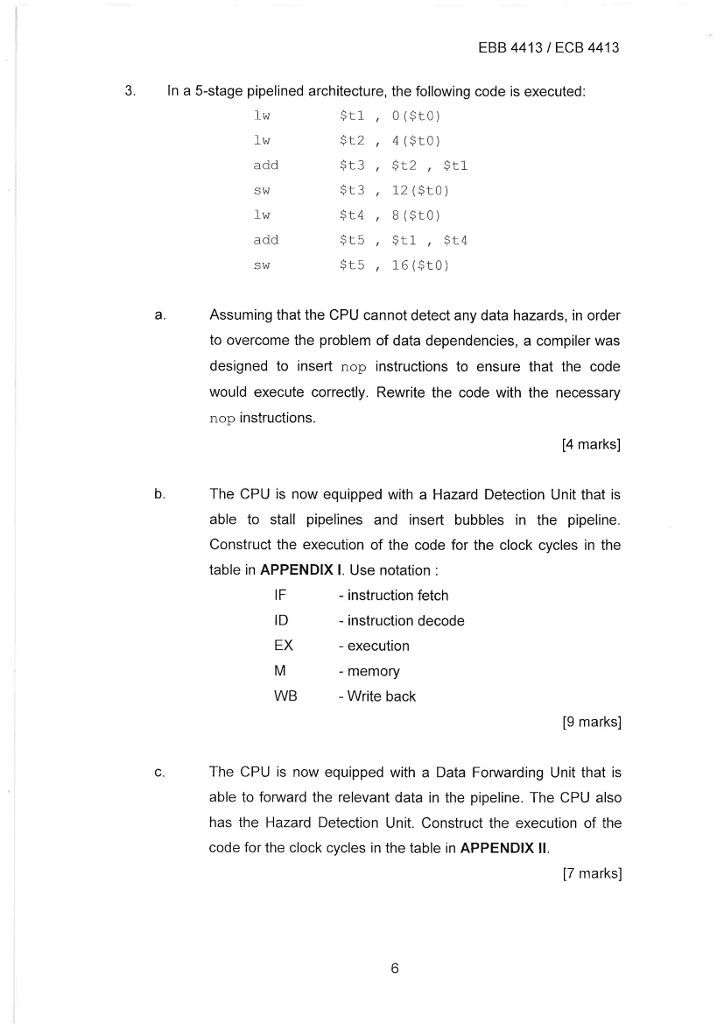

in a 5 stage pipeline architecture, the following code is executed:

lw $t1 , 0($t0) lw $t2 , 4($t0) add $t3 , $t2 , $t1 sw $t3, 12($t0) lw $t4 ,8($t0) add $t5 , $t1 , $t4 sw $t5 , 16($t0)

EBB 4413 ECB 4413 3. In a 5-stage pipelined architecture, the following code is executed tl, 0($t0) $t2, 4 ($t0) $t3, $t2, $t1 $t3, 12 ($t0) $t4, 8 ($t0) add SW add Sw $t5 , 16 ($t0) Assuming that the CPU cannot detect any data hazards, in order to overcome the problem of data dependencies, a compiler was designed to insert nop instructions to ensure that the code would execute correctly. Rewrite the code with the necessary nop instructions [4 marks] The CPU is now equipped with a Hazard Detection Unit that is able to stall pipelines and insert bubbles in the pipeline Construct the execution of the code for the clock cycles in the table in APPENDIX I. Use notation IF ID EX - instruction fetch - instruction decode - execution - memory -Write back WB 9 marks] The CPU is now equipped with a Data Forwarding Unit that is able to forward the relevant data in the pipeline. The CPU also has the Hazard Detection Unit. Construct the execution of the code for the clock cycles in the table in APPENDIX II 7 marks] 6

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts