Question: In a set-associate cache memory system of 64 slots, a 16-bit memory address is decomposed into three fields as below to determine the location of

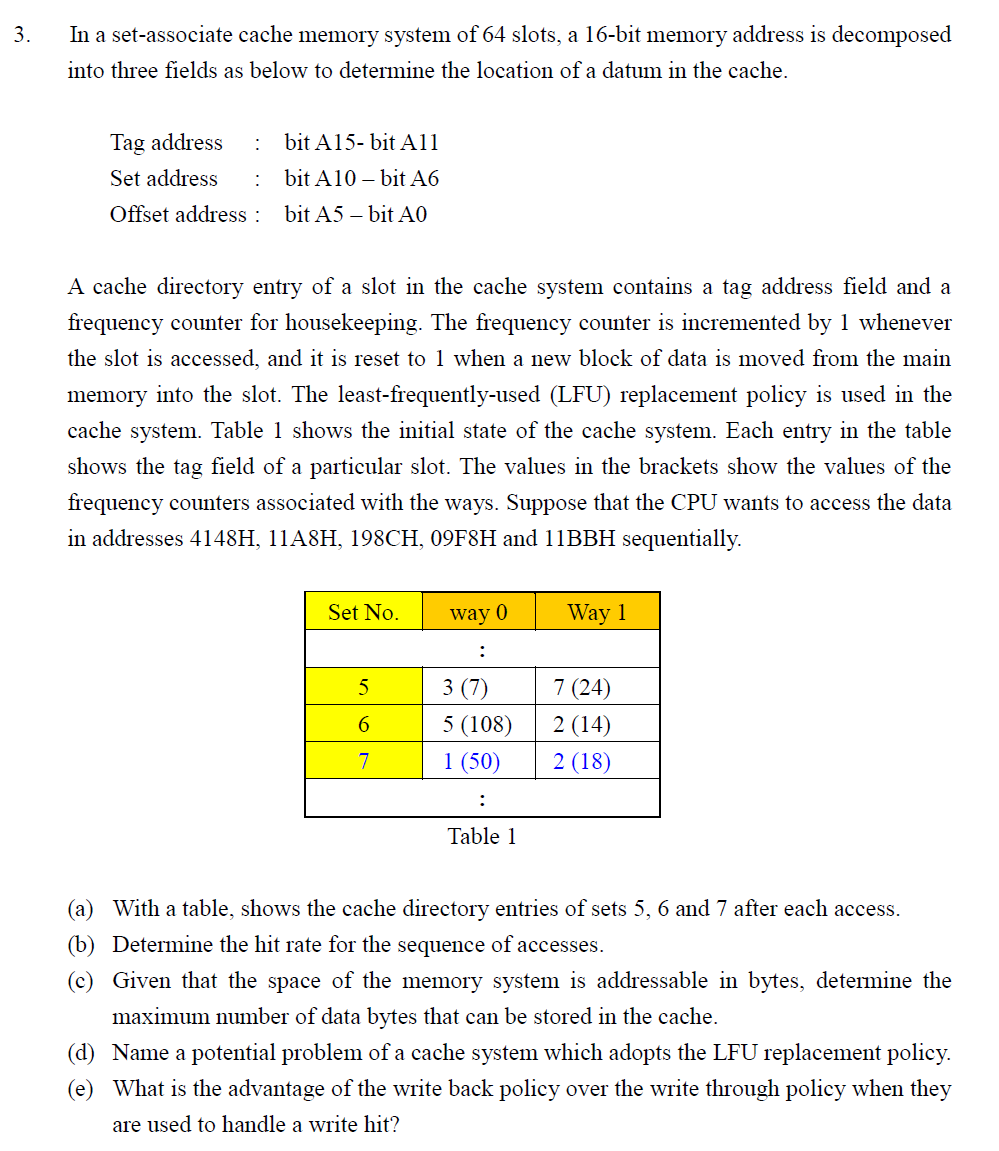

In a set-associate cache memory system of 64 slots, a 16-bit memory address is decomposed into three fields as below to determine the location of a datum in the cache. Tag address : bit A15- bit A11 Set address : bit A 10 - bit A6 Offset address : bit A 5 - bit A 0 A cache directory entry of a slot in the cache system contains a tag address field and a frequency counter for housekeeping. The frequency counter is incremented by 1 whenever the slot is accessed, and it is reset to 1 when a new block of data is moved from the main memory into the slot. The least-frequently-used (LFU) replacement policy is used in the cache system. Table 1 shows the initial state of the cache system. Each entry in the table shows the tag field of a particular slot. The values in the brackets show the values of the frequency counters associated with the ways. Suppose that the CPU wants to access the data in addresses 4148H, 11A8H, 198CH, 09F8H and 11BBH sequentially. (a) With a table, shows the cache directory entries of sets 5, 6 and 7 after each access. (b) Determine the hit rate for the sequence of accesses. (c) Given that the space of the memory system is addressable in bytes, determine the maximum number of data bytes that can be stored in the cache. (d) Name a potential problem of a cache system which adopts the LFU replacement policy. (e) What is the advantage of the write back policy over the write through policy when they are used to handle a write hit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts