Question: In this assignment you will design hardwired control to implement indexed addressing An instruction using indexed addressing has an offset, which is added to the

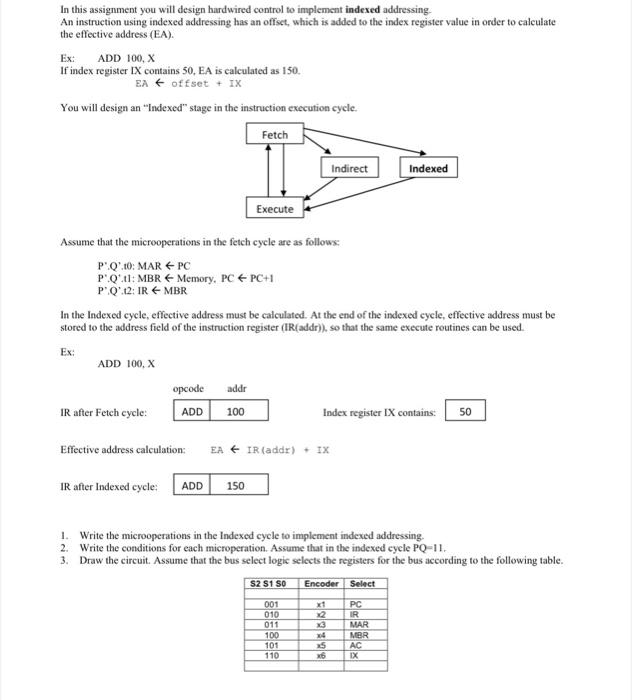

In this assignment you will design hardwired control to implement indexed addressing An instruction using indexed addressing has an offset, which is added to the index register value in order to calculate the effective address (EA). Ex: ADD 100, If index register IX contains 50, EA is calculated as 150. EA offset + IX You will design an "Indexed" stage in the instruction execution cycle. Fetch Indirect Indexed Execute Assume that the microoperations in the fetch cycle are as follows P.Q.10; MARE PC PO 41: MBR Memory. PC +PC+1 PO.12: 1R MBR In the Indexed cycle, effective address must be calculated. At the end of the indexed cycle, effective address must be stored to the address field of the instruction register (IR(addr)), so that the same execute routines can be used Ex: ADD 100, X opcode IR after Fetch cycle Index register IX contains addr ADD 100 50 Effective address calculation: EA IR (addr) - IX IR after Indexed cycle: ADD 150 1. Write the microoperations in the Indexed cycle to implement indexed addressing. 2. Write the conditions for each mieroperation. Assume that in the indexed cycle PQ-11. 3. Draw the circuit. Assume that the bus select logic selects the registers for the bus according to the following table. S2 S1 SO Encoder Select 001 010 011 100 101 110 || 3 PC IR MAR MBR AC IX 25 X6

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts