Question: In this lab, you are going to design 2-bits cascading edge-triggered flip-flops: 1. If your design tool has a D-flip flop, you can use it,

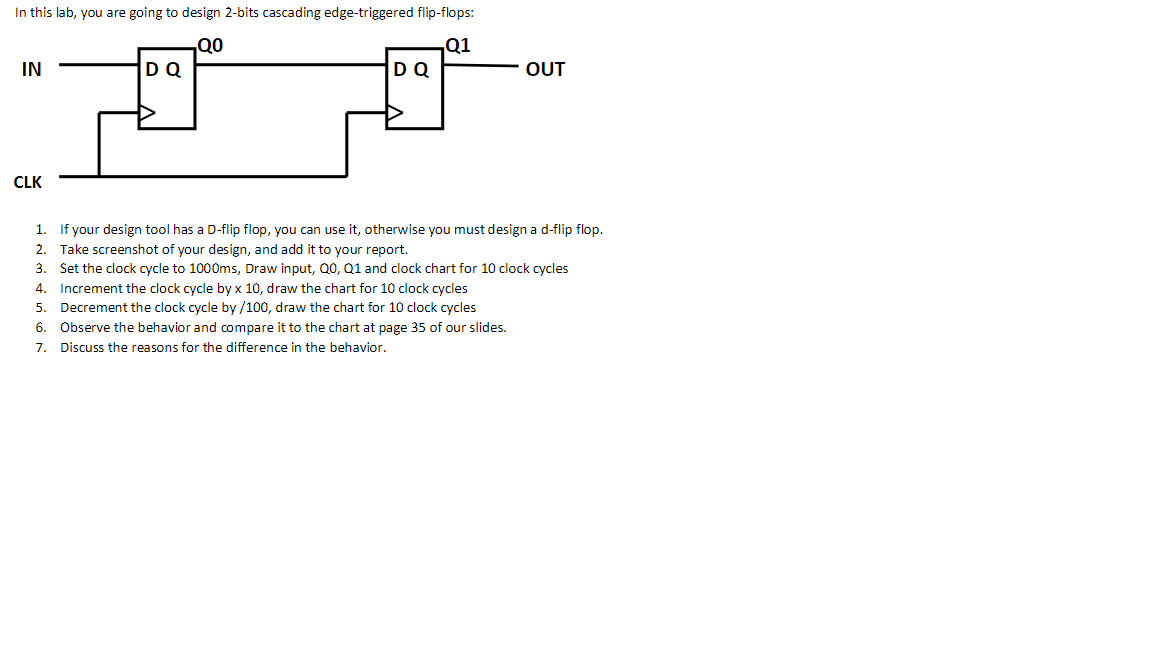

In this lab, you are going to design 2-bits cascading edge-triggered flip-flops: 1. If your design tool has a D-flip flop, you can use it, otherwise you must design a d-flip flop. 2. Take screenshot of your design, and add it to your report. 3. Set the clock cycle to 1000ms, Draw input, Q0, Q1 and clock chart for 10 clock cycles 4. Increment the clock cycle by x10, draw the chart for 10 clock cycles 5. Decrement the clock cycle by /100, draw the chart for 10 clock cycles 6. Observe the behavior and compare it to the chart at page 35 of our slides. 7. Discuss the reasons for the difference in the behavior

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts