Question: In this problem, we will be examining the pipeline shown below. The minimum and maximum delays through the logic are annotated on the figure, and

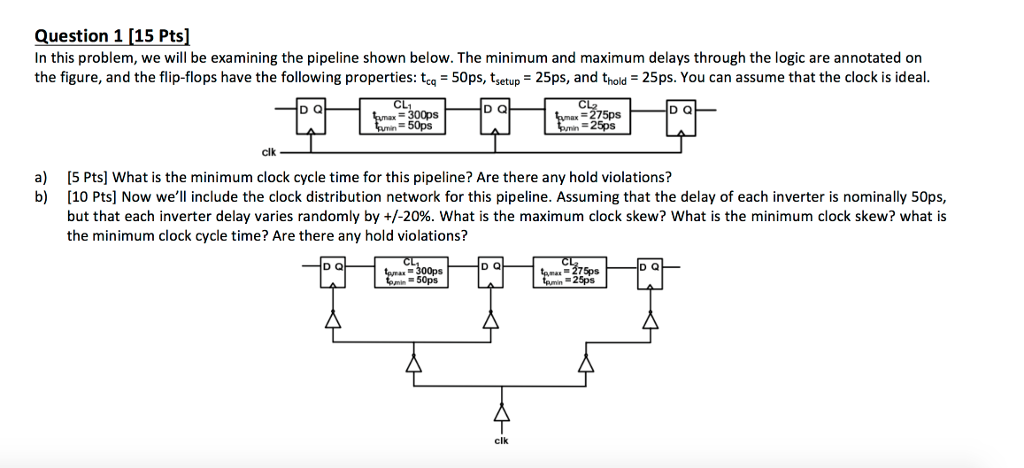

In this problem, we will be examining the pipeline shown below. The minimum and maximum delays through the logic are annotated on the figure, and the flip-flops have the following properties: t_cq = 50ps, t_setup = 25ps, and t_hold = 25ps. You can assume that the clock is ideal. a) What is the minimum clock cycle time for this pipeline? Are there any hold violations? b) Now we'll include the clock distribution network for this pipeline. Assuming that the delay of each inverter is nominally 50ps, but that each inverter delay varies randomly by +/-20%. What is the maximum clock skew? What is the minimum clock skew? what is the minimum clock cycle time? Are there any hold violations

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts