Question: In Verilog (2001) construct a 4x4 register file. Please add comments in the code if there is anything unclear. I would like to see the

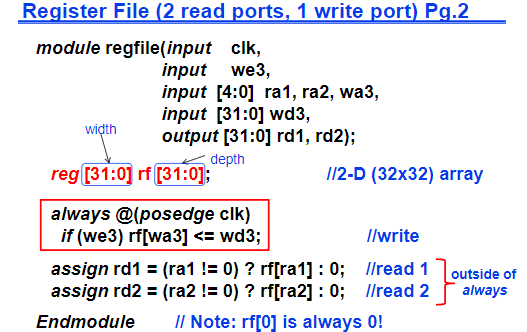

In Verilog (2001) construct a 4x4 register file. Please add comments in the code if there is anything unclear. I would like to see the structural and behavior level descriptions, and a test bench. Please see the attached image as a little reference.

Register File (2 read ports, 1 write port) Pq.2 module regfile(input clk, input we3, input [4:0] ra1, ra2, wa3, input [31:0] wd3, wiothoutput [31:0] rd1, rd2); reg 131:0 r 31:01epth always @(posedge clk) assign rd1 = (ral ! :0) ? rTra1] : 0; 1/read 1 outside of assign rd2+ (ra2 != 0) ? rtlra2] : 0; 1/read 2-always 112-D (32x32) array //write Endmodule INote: rffo1 is always 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts