Question: Inspect the code and create a test bench from the following code in verilog module MY_DESIGN ( Ginl, Gin2, Gout, data1, data2, sel, clk, out1,

Inspect the code and create a test bench from the following code in verilog

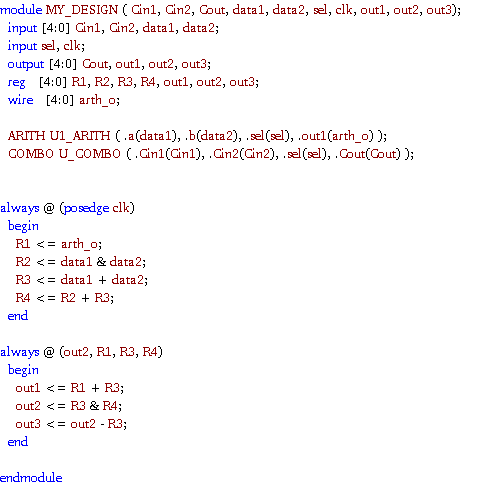

![out1, out2, out3); input [4:0] Gini, Gin2, data1, data 2; input sel,](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f33112efbfd_84266f331129fa76.jpg)

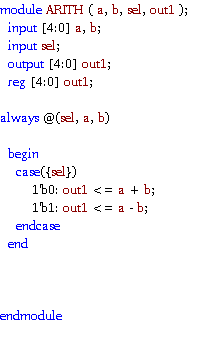

module MY_DESIGN ( Ginl, Gin2, Gout, data1, data2, sel, clk, out1, out2, out3); input [4:0] Gini, Gin2, data1, data 2; input sel, clk; output (4:0) Cout, out1, out2, out3; reg [4:0] R1, R2, R3, R4, outl, out2, out3; wire [4:0] arth_0; ARITH U1_ARITH ( a(datal), .b(data2), sel(el),.outl(arth_o)); COMBO U_COMBO (Ginl(Gini), Gin2(Gin2), sel(sel), Cout(Cout)); always @ (posedge clk) begin R1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts