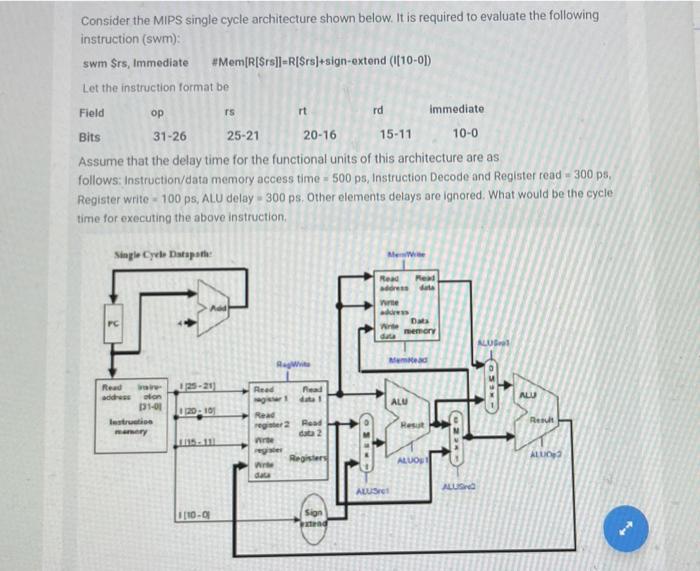

Question: introdctuion to computer Organization Consider the MIPS single cycle architecture shown below. It is required to evaluate the following instruction (swm): swm Srs, Immediate #Mem[R[$rs]=R[$rs]+sign-extend

Consider the MIPS single cycle architecture shown below. It is required to evaluate the following instruction (swm): swm Srs, Immediate #Mem[R[$rs]=R[$rs]+sign-extend (1|10-01) Let the instruction format be Field TS rt rd immediate Bits 31-26 25-21 20-16 15-11 10-0 Assume that the delay time for the functional units of this architecture are as follows: Instruction/data memory access time - 500 ps, Instruction Decode and Register read - 300 ps, Register write - 100 ps, ALU delay - 300 ps Other elements delays are ignored. What would be the cycle time for executing the above instruction Single Cyril Datspot Meat Read ress re D memory data LO Med 15.20 Reed Read ALU ALU Read wa dhe stion 31-01 lestri mary 20-101 Reut OS Resu - | Read og 2 Read data 2 re wer Register ALUD ALUOSI ALUS ALLS 0110-01 Sign Select one: a. 1700 ps b.1600 ps c.None of the given answers d.2000 PS e. 1900 ps SO

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts