Question: it's just true and false not long a) How does the MSP430F5529 go from Low Power Mode to Active Mode and back? (Circle any of

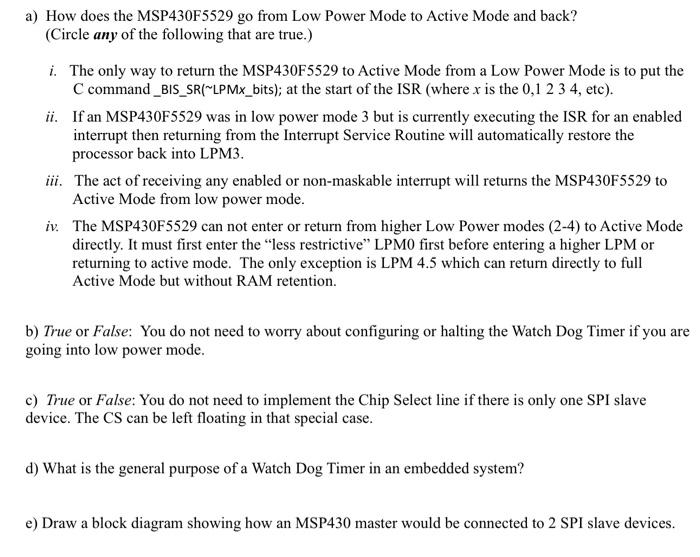

a) How does the MSP430F5529 go from Low Power Mode to Active Mode and back? (Circle any of the following that are true.) i. The only way to return the MSP430F5529 to Active Mode from a Low Power Mode is to put the C command _BIS_SR("LPMx_bits); at the start of the ISR (where x is the 0,1 2 3 4, etc). ii. If an MSP430F5529 was in low power mode 3 but is currently executing the ISR for an enabled interrupt then returning from the Interrupt Service Routine will automatically restore the processor back into LPM3. iii. The act of receiving any enabled or non-maskable interrupt will returns the MSP430F5529 to Active Mode from low power mode. iv. The MSP430F5529 can not enter or return from higher Low Power modes (2-4) to Active Mode directly. It must first enter the "less restrictive" LPMO first before entering a higher LPM or returning to active mode. The only exception is LPM 4.5 which can return directly to full Active Mode but without RAM retention. b) True or False: You do not need to worry about configuring or halting the Watch Dog Timer if you are going into low power mode. c) True or False: You do not need to implement the Chip Select line if there is only one SPI slave device. The CS can be left floating in that special case. d) What is the general purpose of a Watch Dog Timer in an embedded system? e) Draw a block diagram showing how an MSP430 master would be connected to 2 SPI slave devices

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts