Question: k) Multi-threaded software running on multiple cores in parallel is an example of reducing response time via concurrency. 1) In spite of data forwarding the

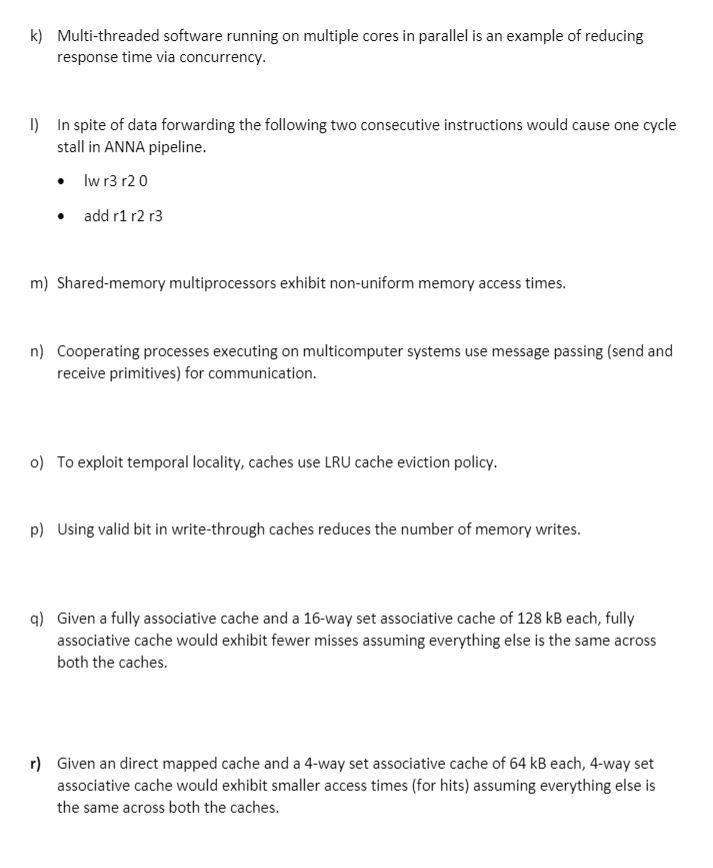

k) Multi-threaded software running on multiple cores in parallel is an example of reducing response time via concurrency. 1) In spite of data forwarding the following two consecutive instructions would cause one cycle stall in ANNA pipeline. lw r3 r20 add r1 r2r3 m) Shared-memory multiprocessors exhibit non-uniform memory access times. in) Cooperating processes executing on multicomputer systems use message passing (send and receive primitives) for communication. o) To exploit temporal locality, caches use LRU cache eviction policy. p) Using valid bit in write-through caches reduces the number of memory writes. a) Given a fully associative cache and a 16-way set associative cache of 128 kB each, fully associative cache would exhibit fewer misses assuming everything else is the same across both the caches. r) Given an direct mapped cache and a 4-way set associative cache of 64 kBeach, 4-way set associative cache would exhibit smaller access times (for hits) assuming everything else is the same across both the caches. k) Multi-threaded software running on multiple cores in parallel is an example of reducing response time via concurrency. 1) In spite of data forwarding the following two consecutive instructions would cause one cycle stall in ANNA pipeline. lw r3 r20 add r1 r2r3 m) Shared-memory multiprocessors exhibit non-uniform memory access times. in) Cooperating processes executing on multicomputer systems use message passing (send and receive primitives) for communication. o) To exploit temporal locality, caches use LRU cache eviction policy. p) Using valid bit in write-through caches reduces the number of memory writes. a) Given a fully associative cache and a 16-way set associative cache of 128 kB each, fully associative cache would exhibit fewer misses assuming everything else is the same across both the caches. r) Given an direct mapped cache and a 4-way set associative cache of 64 kBeach, 4-way set associative cache would exhibit smaller access times (for hits) assuming everything else is the same across both the caches

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts