Question: && Lab 5 : part 3 Design state machine with Mealy and Moore outputs. Lab 5 - 3 Objective: Design Sequence detector, state machine with

&&

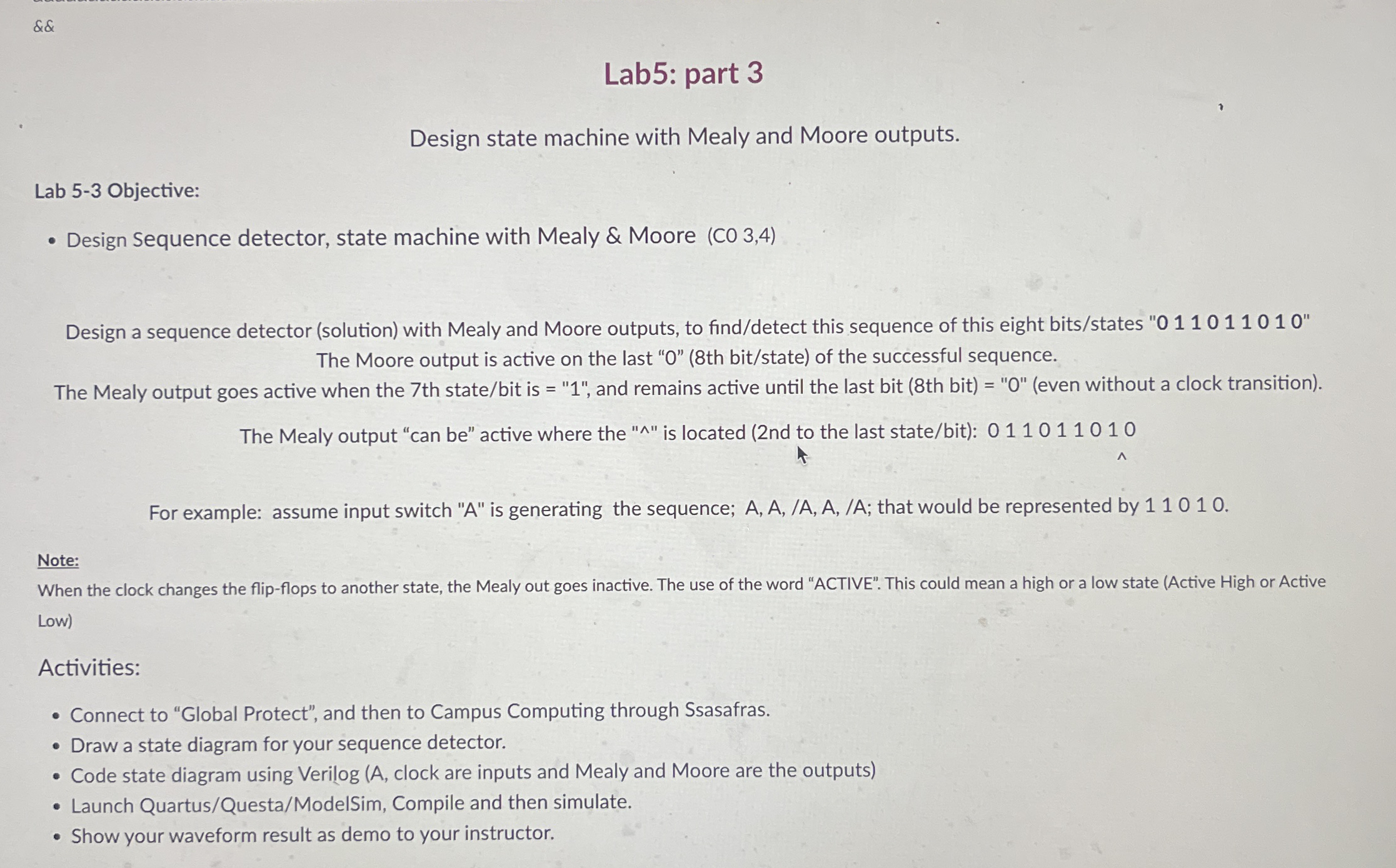

Lab: part

Design state machine with Mealy and Moore outputs.

Lab Objective:

Design Sequence detector, state machine with Mealy & Moore CO

Design a sequence detector solution with Mealy and Moore outputs, to finddetect this sequence of this eight bitsstates The Moore output is active on the last th bitstate of the successful sequence.

The Mealy output goes active when the th statebit is and remains active until the last bit th biteven without a clock transition

The Mealy output "can be active where the is located nd to the last statebit:

For example: assume input switch A is generating the sequence; ; that would be represented by

Note:

When the clock changes the flipflops to another state, the Mealy out goes inactive. The use of the word "ACTIVE". This could mean a high or a low state Active High or Active Low

Activities:

Connect to "Global Protect", and then to Campus Computing through Ssasafras.

Draw a state diagram for your sequence detector.

Code state diagram using Verilog A clock are inputs and Mealy and Moore are the outputs

Launch QuartusQuestaModelSim Compile and then simulate.

Show your waveform result as demo to your instructor.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock