Question: Lab report: put what you have finished in running testbench into the lab report, totally at least three pages, need to explain your understanding of

Lab report: put what you have finished in running testbench into the lab report, totally at least three pages, need to

explain your understanding of the code, how you run the code and need to put the screenshot in it.

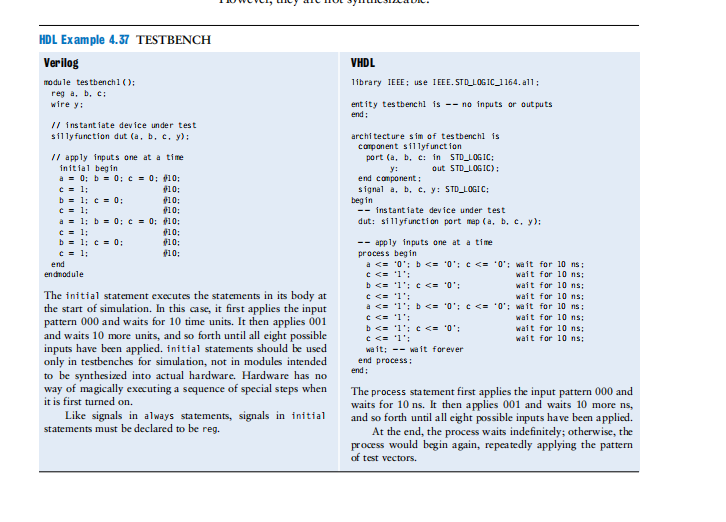

Verilog

module testbench1 ();

reg a, b, c;

wire y;

// instantiate device under test

sillyfunction dut (a, b, c, y);

// apply inputs one at a time

initial begin

a = 0; b= 0; c = 0; #10;

c =1; #10;

b =1; c= 0; #10;

c =1; #10;

a =1; b= 0; c= 0; #10;

c =1; #10;

b =1; c =0; #10;

c =1; #10;

end

endmodule

The initial statement executes the statements in its body at

the start of simulation. In this case, it first applies the input

pattern 000 and waits for 10 time units. It then applies 001

and waits 10 more units, and so forth until all eight possible

inputs have been applied. initial statements should be used

only in testbenches for simulation, not in modules intended

to be synthesized into actual hardware. Hardware has no

way of magically executing a sequence of special steps when

it is first turned on.

Like signals in always statement, signals in initial statement must be declared to be reg.

VHDL

library IEEE; use IEEE.STD_LOGIC_1164.all;

entity testbench1 is no inputs or outputs

end;

architecture sim of testbench1 is

component sillyfunction

port (a, b, c: in STD_LOGIC;

y: out STD_LOGIC);

end component;

signal a, b, c, y: STD_LOGIC;

begin

instantiate device under test

dut: sillyfunction port map (a, b, c, y);

apply inputs one at a time

process begin

a

c

b

c

A

C

B

wait; wait forever

end process;

end;

The process statement first applies the input pattern 000 and

waits for 10 ns. It then applies 001 and waits 10 more ns,

and so forth until all eight possible inputs have been applied.

At the end, the process waits indefinitely; otherwise, the

process would begin again , repeatedly applying the pattern of test vectors.

VHDL HDL Example 4.37 TESTBENCH Verilog module testbench 1(); reg a, b, c: wire y: library IEEE; use IEEE. STD_LOGIC_1164. all; entity testbenchl is -- no inputs or outputs end: 17 instantiate device under test silly function dut (a, b, c, y): // apply inputs one at a time initial begin a = 0; b = 0; c = 0; 110: C = 1; 010: b = 1; C = 0; 110: C = 1: 110: a = 1; b = 0; c = 0; 010: C = 1: 010: b = 1; c = 0; 110: C = 1; 110: end endmodule architecture sim of testbenchl is component sillyfunction port (a, b, c in STD_LOGIC; y: out STD_LOGIC): end component: signal a, b, c, y: STD_LOGIC: begin -- instantiate device under test dut: sillyfunction port map (a, b, c, y): The initial statement executes the statements in its body at the start of simulation. In this case, it first applies the input pattern 000 and waits for 10 time units. It then applies 001 and waits 10 more units, and so forth until all eight possible inputs have been applied. initial statements should be used only in testbenches for simulation, not in modules intended to be synthesized into actual hardware. Hardware has no way of magically executing a sequence of special steps when it is first turned on. Like signals in always statements, signals in initial statements must be declared to be reg. -- apply inputs one at a time process begin a

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts