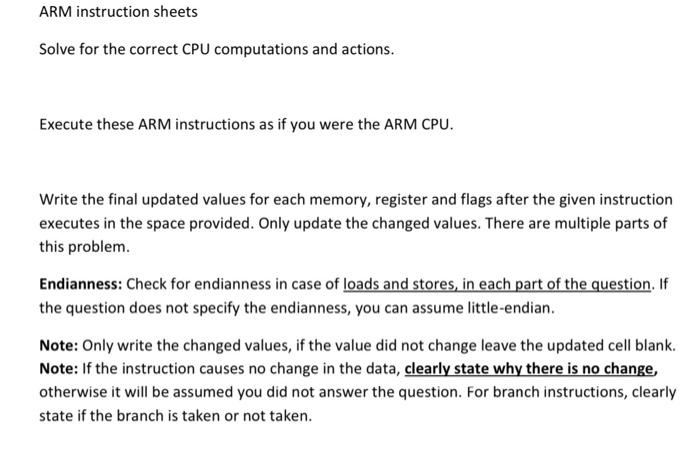

Question: LDR R5, [R4, #4] specific answer needed do not answer if you do not know Q1.6 LDR R5, [R4, #41 ; big endian Memory Address

![LDR R5, [R4, #4] specific answer needed do not answer if you](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f3ac28952c1_35266f3ac281f0f1.jpg)

Q1.6 LDR R5, [R4, #41 ; big endian Memory Address Orig. Updated Data Updated Data Ox84F0 Ox841 Ox84F2 Ox84F3 Data Ox82 0x32 OxBC Ox84F4 0x8455 Ox84F6 Ox84F7 0x84F8 Ox84F9 0x84 FA Ox84FB Ox84 FC Ox84FD Ox84 FE Ox84FF Ox8500 Ox8501 Ox8502 Ox8503 Ox8504 Ox8505 Ox8506 Ox8507 OxA4 0xF4 0x6A Ox9D OxC2 0x42 Ox67 OxD 0XA1 OxF2 OxBB Ox5E OXEE OXFA OxF3 Ox54 Register RO R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15 Orig. Data OxDC002B45 Ox00008500 OxABO3873C Ox2B78DFEO 0x000084F0 Ox00100000 Ox041 BOCOD Ox00100000 Ox00000000 Ox00842 ABO OxOABD9830 Ox0000000A Ox00000002 OX00008500 Ox003762DD Ox00100000 0 1 Flags N Z V Q 1 OO N/A Ox8508 0x8509 Ox850A Ox850B Ox850C Ox850D Ox850E Ox850F OxBA Ox6D Ox9C Ox78 OxBB Oxc3 OxB4 OxAA OxD9 OXDA OxFF OxE5 Ox33 ARM instruction sheets Solve for the correct CPU computations and actions. Execute these ARM instructions as if you were the ARM CPU. Write the final updated values for each memory, register and flags after the given instruction executes in the space provided. Only update the changed values. There are multiple parts of this problem. Endianness: Check for endianness in case of loads and stores, in each part of the question. If the question does not specify the endianness, you can assume little-endian. Note: Only write the changed values, if the value did not change leave the updated cell blank. Note: If the instruction causes no change in the data, clearly state why there is no change, otherwise it will be assumed you did not answer the question. For branch instructions, clearly state if the branch is taken or not taken

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts