Question: Low Battery Your Mac will sleep soon unless plugged Close into a power outlet EEEE-220 Lab5 1 From mycourses download on your desktop this pdf

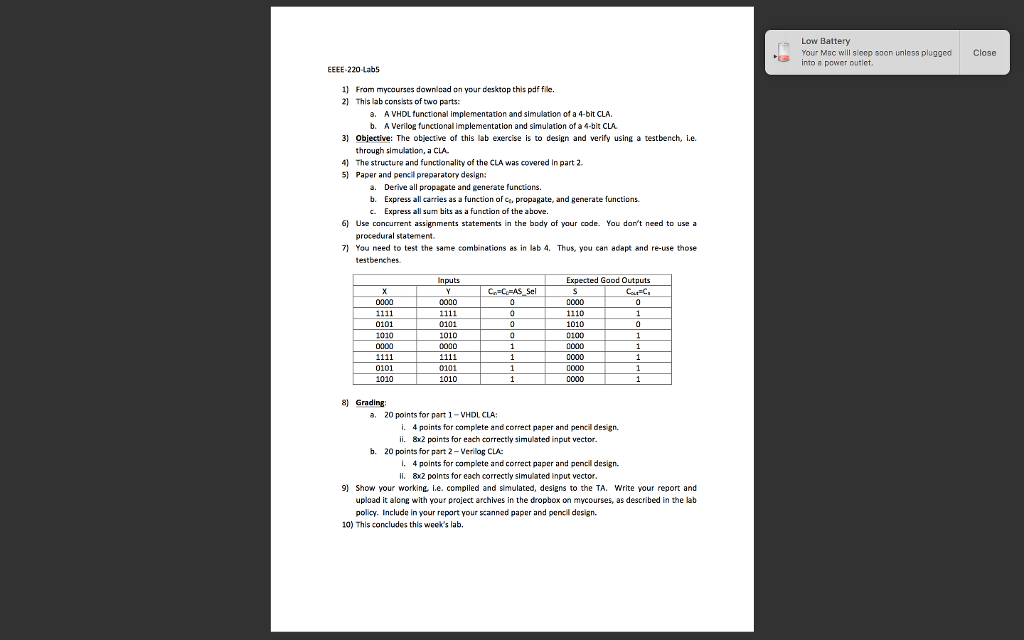

Low Battery Your Mac will sleep soon unless plugged Close into a power outlet EEEE-220 Lab5 1 From mycourses download on your desktop this pdf file. 2 This lab consists of two parts: a. b. AVHDL functional implementation and simulation of a 4-bit CLA. A Verilog functional implementation and simulation of a 4-bit CLA 3 Objective: The objective of this lab exercise is to design and verify using a testbench, .e. through simulation, a CLA 4) The structure and functionality of the CLA was covered in part 2 5) Paper and pencil preparatory design: a. Derive all propagate and generate functions. b. Express all carries as a function of c, propagate, and generate functions c. Express all sum bits as a function af the above 6) Use concurrent assignments statements in the body of your code. You dot need to use a procedural statement 7) You need to test the same combinations as in lab 4. Thus, you can adapt and re-use those Expected Gaod Outputs 1110 1010 0101 0101 0101 1010 0101 8) Grading a. 20 points for part 1-VHDL CLA i. 4 points for complete and correct paper and pencil design. ii. 8x2 points for each correctly simulated input vector b. 20 points for part 2-Verilog CLA: i. 4 points for complete and correct paper and pencl design. ii. 8x2 points foreach correctly simulated input vector 9) Show your working e. compiled and simulated, designs to the TA. Write your report and upload it along with your project archives in the dropbox on mycourses, as described in the lab policy. Include in your report your scanned paper and pencil design 10) This concludes this week's lab. Low Battery Your Mac will sleep soon unless plugged Close into a power outlet EEEE-220 Lab5 1 From mycourses download on your desktop this pdf file. 2 This lab consists of two parts: a. b. AVHDL functional implementation and simulation of a 4-bit CLA. A Verilog functional implementation and simulation of a 4-bit CLA 3 Objective: The objective of this lab exercise is to design and verify using a testbench, .e. through simulation, a CLA 4) The structure and functionality of the CLA was covered in part 2 5) Paper and pencil preparatory design: a. Derive all propagate and generate functions. b. Express all carries as a function of c, propagate, and generate functions c. Express all sum bits as a function af the above 6) Use concurrent assignments statements in the body of your code. You dot need to use a procedural statement 7) You need to test the same combinations as in lab 4. Thus, you can adapt and re-use those Expected Gaod Outputs 1110 1010 0101 0101 0101 1010 0101 8) Grading a. 20 points for part 1-VHDL CLA i. 4 points for complete and correct paper and pencil design. ii. 8x2 points for each correctly simulated input vector b. 20 points for part 2-Verilog CLA: i. 4 points for complete and correct paper and pencl design. ii. 8x2 points foreach correctly simulated input vector 9) Show your working e. compiled and simulated, designs to the TA. Write your report and upload it along with your project archives in the dropbox on mycourses, as described in the lab policy. Include in your report your scanned paper and pencil design 10) This concludes this week's lab

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts