Question: Memory Hierarchy. Consider a processor with the following memory organization: L1 Cache, L2 Cache, L3 Cache and main memory. Each cache stores both tags and

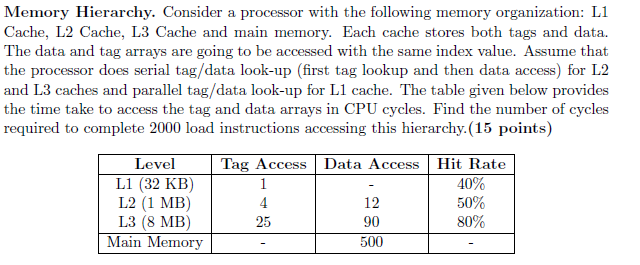

Memory Hierarchy. Consider a processor with the following memory organization: L1 Cache, L2 Cache, L3 Cache and main memory. Each cache stores both tags and data. The data and tag arrays are going to be accessed with the same index value. Assume that the processor does serial tag/data look-up (first tag lookup and then data access) for L2 and L3 caches and parallel tag/data look-up for L1 cache. The table given below provides the time take to access the tag and data arrays in CPU cycles. Find the number of cycles required to complete 2000 load instructions accessing this hierarchy. (15 points) Level L1 (32 KB) L2 (1 MB) L3 (8 MB) Main Memory Tag Access Data Access |Hit Rate 12 90 500 40% 50% 80% 25 Memory Hierarchy. Consider a processor with the following memory organization: L1 Cache, L2 Cache, L3 Cache and main memory. Each cache stores both tags and data. The data and tag arrays are going to be accessed with the same index value. Assume that the processor does serial tag/data look-up (first tag lookup and then data access) for L2 and L3 caches and parallel tag/data look-up for L1 cache. The table given below provides the time take to access the tag and data arrays in CPU cycles. Find the number of cycles required to complete 2000 load instructions accessing this hierarchy. (15 points) Level L1 (32 KB) L2 (1 MB) L3 (8 MB) Main Memory Tag Access Data Access |Hit Rate 12 90 500 40% 50% 80% 25

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts