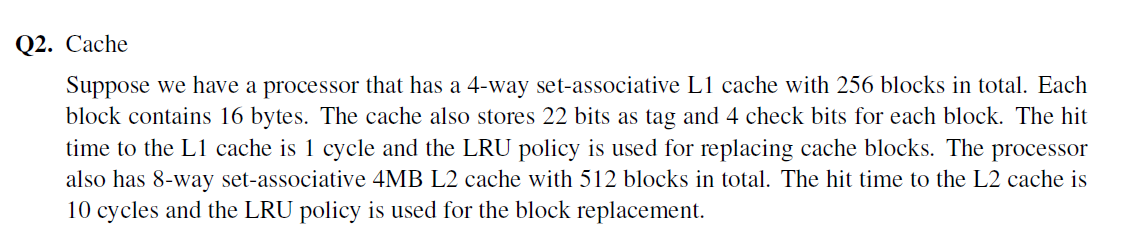

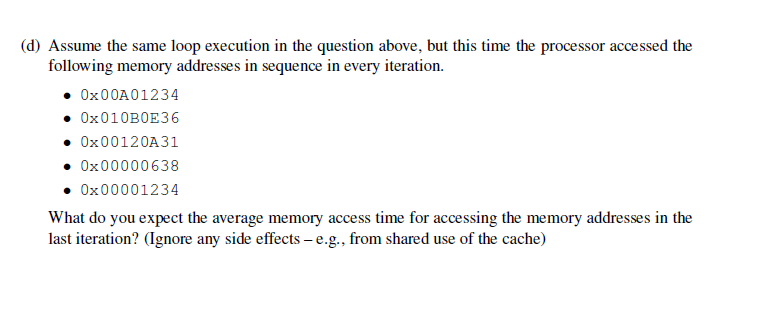

Question: Q2. Cache Suppose we have a processor that has a 4-way set-associative L1 cache with 256 blocks in total. Each block contains 16 bytes. The

Q2. Cache Suppose we have a processor that has a 4-way set-associative L1 cache with 256 blocks in total. Each block contains 16 bytes. The cache also stores 22 bits as tag and 4 check bits for each block. The hit time to the L1 cache is 1 cycle and the LRU policy is used for replacing cache blocks. The processor also has 8-way set-associative 4MB L2 cache with 512 blocks in total. The hit time to the L2 cache is 10 cycles and the LRU policy is used for the block replacement. (d) Assume the same loop execution in the question above, but this time the processor accessed the following memory addresses in sequence in every iteration. 0x00A01234 0x010B0E36 . 0x00120A31 0x00000638 . 0x00001234 What do you expect the average memory access time for accessing the memory addresses in the last iteration? (Ignore any side effects - e.g., from shared use of the cache)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts