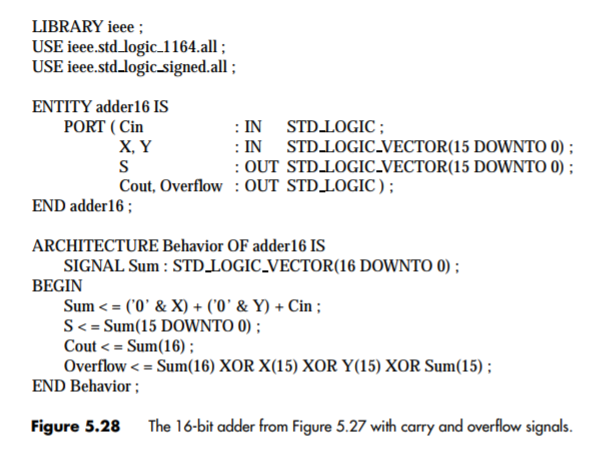

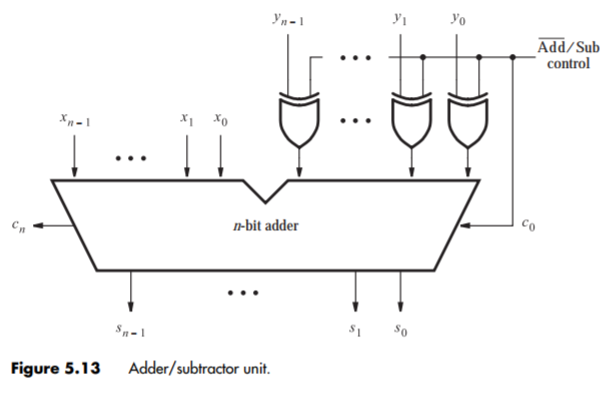

Question: Modify the VHDL code from Figure 5.28 to implement the ASU represented in Figure 5.13. Create a file ASU.vhd to accomplish this task. Note: change

Modify the VHDL code from Figure 5.28 to implement the ASU represented in Figure 5.13. Create a file ASU.vhd to accomplish this task.

Note: change ieee.std_logic_signed.all to ieee.std_logic_unsigned.all.

Can you please help me modify the code? And it'll be great help and much appreciated if you could explain it, too? Thank you so much!

LIBRARY ieee USE ieee.std logic.1164.all USE ieee.std logic-signed.all; ENTITY adder16 IS IN STDLOGIC IN STDLOGIC-VECTOR(15 DOWNTO 0); OUT STDLOGIC-VECTOR(15 DOWNTO 0); PORT (Cin X, Y Cout, Overflow OUT STD LOGIC) END adder16; ARCHITECTURE Behavior OF adder16 IS BEGIN SIGNAL Sum : STD_LOGIC.VECTOR(16 DOWNTO 0) Sum

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts