Question: Need help with Computer Architecture homework, we're using this book Computer Organization and Design, ARM Edition ISBN 978-0-12-801733-3. Consider the code segment in RISC-V which

Need help with Computer Architecture homework, we're using this book Computer Organization and Design, ARM Edition ISBN 978-0-12-801733-3.

Consider the code segment in RISC-V which is similar to LEGv8

fld f0, 0(x0) ; load f0 from address 0+x0

Loop: fld f2, 0(x2) ; load f2 from address 0+x2

fmult f2, f2, f0 ; f2 = f2 * f0

fsd f2, 0(x2) ; store x2 at address 0+x2

addwi x2, x2, 8 ; x2 = x2 +8

subwi x4, x3, x2 ; x4 = x3 x2

bne x4, x0, loop ; branch to loop if x4!= 0

Assume the initial value of x3 is x2 + 64. Assume x0 =0 and x2=16, and the memory contains:

| M[0] | M[8] | M[16] | M[24] | M[32] | M[40] | M[48] | M[56] | M[64] | M[72] | M[80] | M[88] |

| 4.0 | 1.0 | 7.0 | 9.0 | 5.0 | 3.0 | 1.0 | 2.0 | 5.0 | 8.0 | 7.0 | 3.0 |

0 8 16 24 32 40 48 56 64 72 80

The cache size is 64 bytes and the block size is 16 bytes. Make a table similar with Example 5 in Lecture slides.

A) Display the content of memory, cache hit or miss status, and the content of cache as the loop executes, assuming the cache is direct mapped, with write through and no write allocate.

Repeat Part (a) assuming cache is a 2-way set associative, with FIFO replacement policy, and write back, and write allocate.

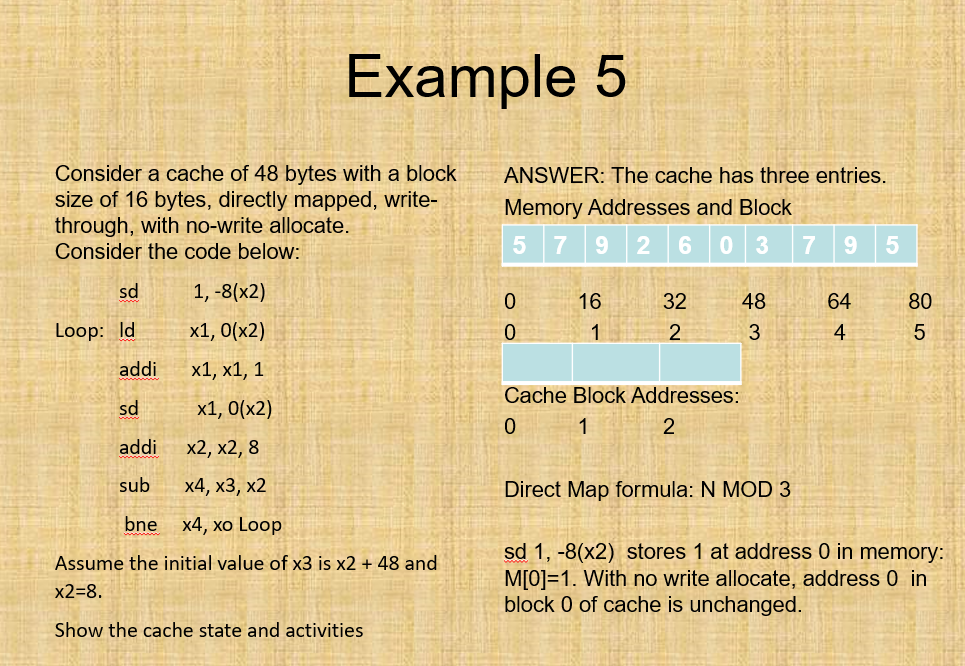

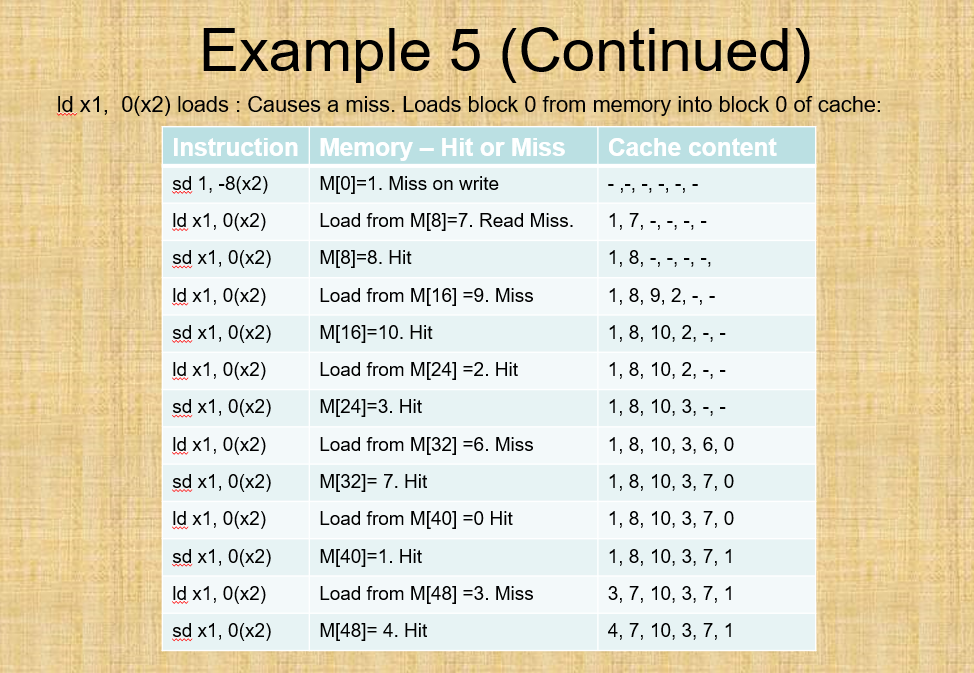

Example 5 Consider a cache of 48 bytes with a block size of 16 bytes, directly mapped, write- through, with no-write allocate. Consider the code below ANSWER: The cache has three entries. Memory Addresses and Block 5 7 9 2 6 037 9 5 sd 1,-8(x2) 0 16 32 48 64 80 0 Loop: ldx1, 0(x2) 2 3 4 addi x1, x1, 1 sdx1, 0(x2) addi x2, x2, 8 sub x4, x3, x2 bne x4, xo Loop Cache Block Addresses: 2 Direct Map formula: N MOD 3 Assume the initial value of x3 is x2 + 48 and sd 1, -8(x2) stores 1 at address 0 in memory: x2-8 M[0j-1. With no write allocate, address 0 in block 0 of cache is unchanged. Show the cache state and activities Example 5 Consider a cache of 48 bytes with a block size of 16 bytes, directly mapped, write- through, with no-write allocate. Consider the code below ANSWER: The cache has three entries. Memory Addresses and Block 5 7 9 2 6 037 9 5 sd 1,-8(x2) 0 16 32 48 64 80 0 Loop: ldx1, 0(x2) 2 3 4 addi x1, x1, 1 sdx1, 0(x2) addi x2, x2, 8 sub x4, x3, x2 bne x4, xo Loop Cache Block Addresses: 2 Direct Map formula: N MOD 3 Assume the initial value of x3 is x2 + 48 and sd 1, -8(x2) stores 1 at address 0 in memory: x2-8 M[0j-1. With no write allocate, address 0 in block 0 of cache is unchanged. Show the cache state and activities

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts