Question: NEED VHDL DESIGN CODE, TESTBENCH CODE AND WAVEFORMS Problem 3: (10 pts) Design a 24-bit I-Type instruction register. This design is similar to problem 2

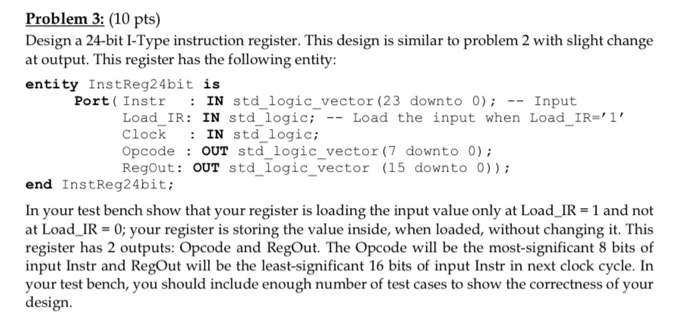

Problem 3: (10 pts) Design a 24-bit I-Type instruction register. This design is similar to problem 2 with slight change at output. This register has the following entity: entity InstReg24bit is Port ( Instr : IN std_logic_vector (23 downto 0); -- Input Load_IR: IN std logic; -- Load the input when Load_IR='1' Clock : IN std_logic; Opcode : OUT std_logic_vector (7 downto 0); Regout: OUT std_logic_vector (15 downto 0)); end InstReg24bit; In your test bench show that your register is loading the input value only at Load_IR = 1 and not at Load_IR = 0; your register is storing the value inside, when loaded, without changing it. This register has 2 outputs: Opcode and RegOut. The Opcode will be the most significant 8 bits of input Instr and RegOut will be the least-significant 16 bits of input Instr in next clock cycle. In your test bench, you should include enough number of test cases to show the correctness of your design

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts