Question: OBJECTIVE: In C, calculate the performance of a program with dependent arithmetic instructions, by simulating the execution on (i) a simple 6-stage pipeline architecture; (ii)

OBJECTIVE:

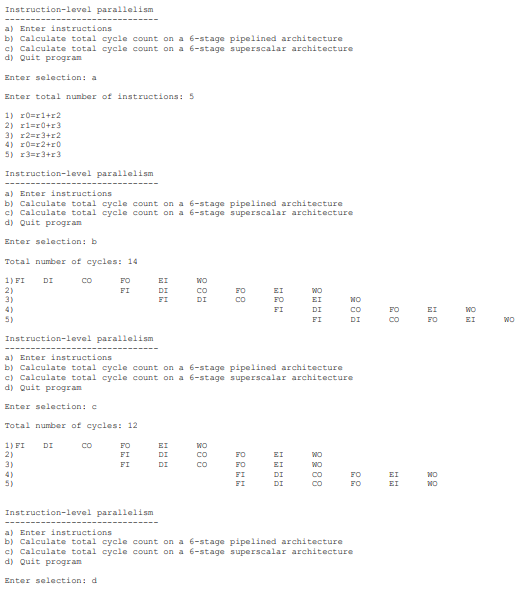

In C, calculate the performance of a program with dependent arithmetic instructions, by simulating the execution on (i) a simple 6-stage pipeline architecture; (ii) a superscalar 6- stage architecture of degree 2 (2 sets of functional units). The six stages are: Fetch Instruction (FI), Decode Instruction (DI), Calculate Operands (CO), Fetch Operands (FO), Execute Instructions (EI), and Write Output (WO).

INPUTS:

- Number of instructions in the program

- Set of automatically numbered instructions containing arithmetic register assignments

- Architecture to simulate program on (pipelined, superscalar)

OUTPUTS:

- The total cycle count for the program

- A Gantt chart of the pipelined stages of the instructions

SPECIFICATIONS:

The program calculates the performance of a set of arithmetic register assignment statements and prints out the aligned pipelined instructions based on choosing from a menu of choices, where each choice calls the appropriate procedure:

a) Enter instructions

b) Calculate total cycle count on a 6-stage pipelined architecture

c) Calculate total cycle count on a 6-stage superscalar architecture

d) Quit program

-------------------------------------------------------------------------------------------

SAMPLE OUTPUT (SHOW YOURS WORKS LIKE THIS)

-------------------------------------------------------------------------------------------

Instruction-level parallelism a) Enter instructions b) Calculate total cycle count on a 6-stage pipelined architecture c) Calculate total cycle count on a 6-stage superscalar architecture d) Quit progran Enter selection: a Enter total nunber of instructions: 5 1) 2) 3) r0 r1+r2 r1=r0+r3 r2=r1+r2 5) r3=r2+r3 Instruction-level parallelism a) Enter instructions b) Calculate total cycle count on a 6-stage pipelined architecture c) Calculate total cycle count on a 6-stage superscalar architecture d) Quit progran Enter selection: b Total number of cycles: 14 1)F D 21 EI DI EI Instruction-level parallelism a) Enter instructions b) Calculate total cycle count on a 6-stage pipelined architecture c) Calculate total cycle count on a 6-stage superscalar architecture d) Quit progran Enter selection: c Total number of cycles: 12 1)FI DI EI EI Instruction-level parallelism a) Enter instructions b) Calculate total cycle count on a 6-stage pipelined architecture c) Calculate total cycle count on a 6-stage superscalar architecture d) Quit progran Enter selection: d

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts