Question: ONLY USING VHDL PLEASE DO NOT USE VERILOG: In the block diagram given below inputs are fed into the first row of ALU blocks as

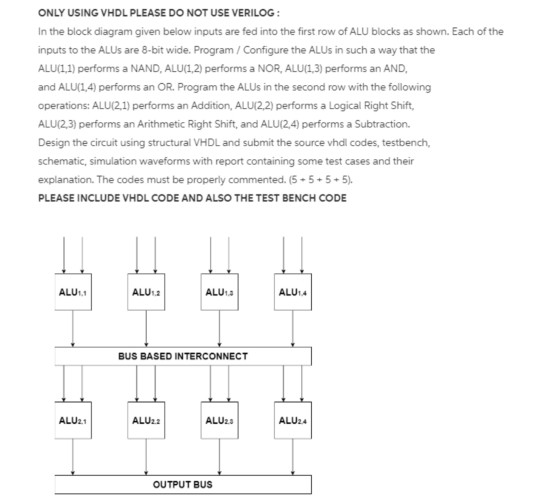

ONLY USING VHDL PLEASE DO NOT USE VERILOG: In the block diagram given below inputs are fed into the first row of ALU blocks as shown. Each of the inputs to the ALUs are 8-bit wide. Program / Configure the ALUS in such a way that the ALU(1.1) performs a NAND, ALU(1.2 performs a NORALULL. 3) performs an AND, and ALU(1.4 performs an OR. Program the ALUs in the second row with the following operations: ALU(2.1) performs an Addition, ALU122) performs a Logical Right Shift, ALU(2,3) performs an Arithmetic Right Shift and ALUI2.4 performs a Subtraction Design the circuit using structural VHDL and submit the source vhdi codes, testbench, schematic, simulation waveforms with report containing some test cases and their explanation. The codes must be properly commented. (5-5-5-5). PLEASE INCLUDE VHDL CODE AND ALSO THE TEST BENCH CODE ALUU ALUA BUS BASED INTERCONNECT ALU23 OUTPUT BUS ONLY USING VHDL PLEASE DO NOT USE VERILOG: In the block diagram given below inputs are fed into the first row of ALU blocks as shown. Each of the inputs to the ALUs are 8-bit wide. Program / Configure the ALUS in such a way that the ALU(1.1) performs a NAND, ALU(1.2 performs a NORALULL. 3) performs an AND, and ALU(1.4 performs an OR. Program the ALUs in the second row with the following operations: ALU(2.1) performs an Addition, ALU122) performs a Logical Right Shift, ALU(2,3) performs an Arithmetic Right Shift and ALUI2.4 performs a Subtraction Design the circuit using structural VHDL and submit the source vhdi codes, testbench, schematic, simulation waveforms with report containing some test cases and their explanation. The codes must be properly commented. (5-5-5-5). PLEASE INCLUDE VHDL CODE AND ALSO THE TEST BENCH CODE ALUU ALUA BUS BASED INTERCONNECT ALU23 OUTPUT BUS

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts