Question: Parameters Your goal is to determine the minimal parameterization for a BTB ( Figure 1 ) such that the performance of a fixed branch penalty

Parameters

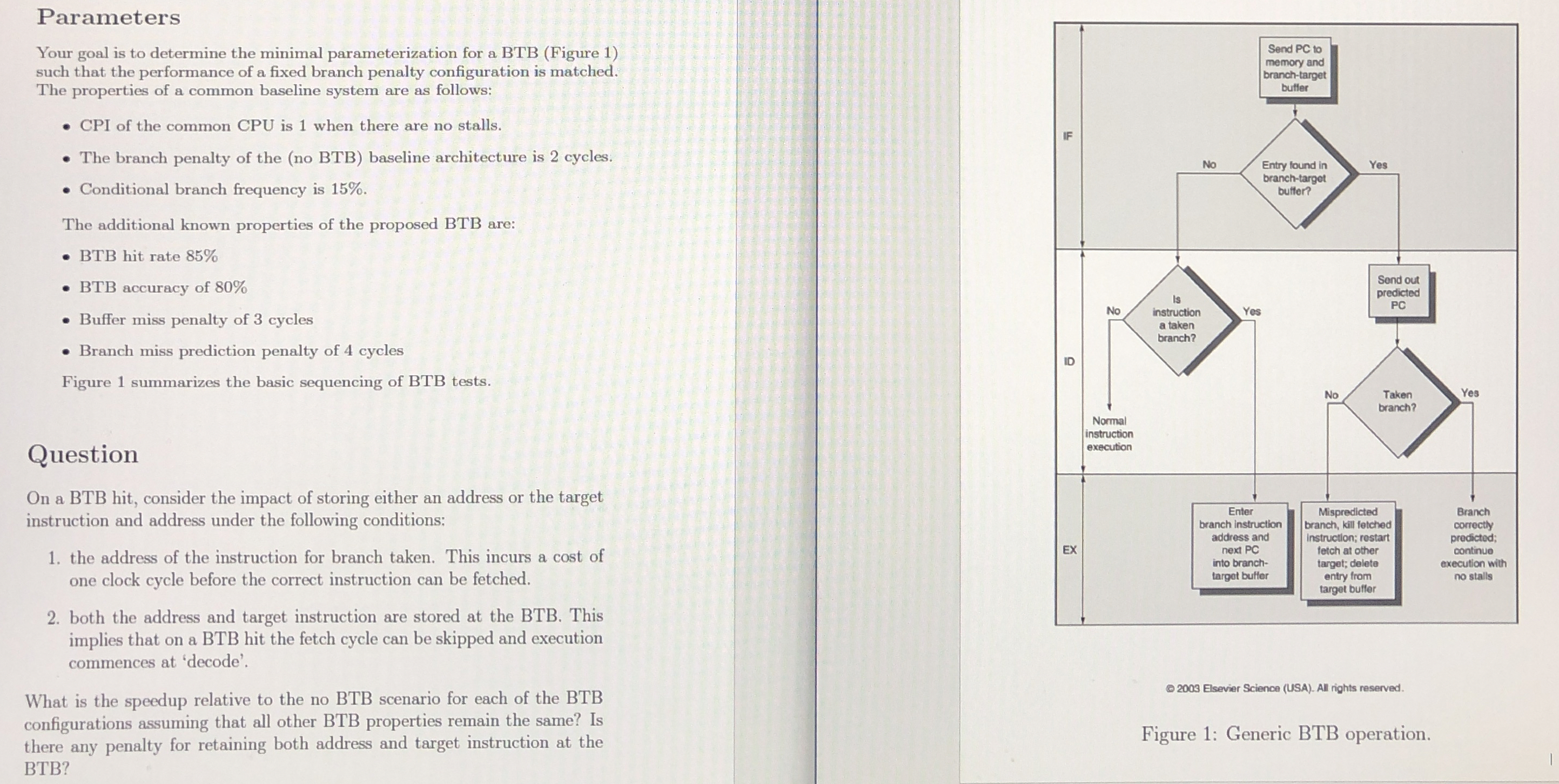

Your goal is to determine the minimal parameterization for a BTB Figure such that the performance of a fixed branch penalty configuration is matched. The properties of a common baseline system are as follows:

CPI of the common CPU is when there are no stalls.

The branch penalty of the no BTB baseline architecture is cycles.

Conditional branch frequency is

The additional known properties of the proposed BTB are:

BTB hit rate

BTB accuracy of

Buffer miss penalty of cycles

Branch miss prediction penalty of cycles

Figure summarizes the basic sequencing of BTB tests.

Question

On a BTB hit, consider the impact of storing either an address or the target instruction and address under the following conditions:

the address of the instruction for branch taken. This incurs a cost of one clock cycle before the correct instruction can be fetched.

both the address and target instruction are stored at the BTB This implies that on a BTB hit the fetch cycle can be skipped and execution commences at 'decode'.

What is the speedup relative to the no BTB scenario for each of the BTB configurations assuming that all other BTB properties remain the same? Is there any penalty for retaining both address and target instruction at the BTB

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock