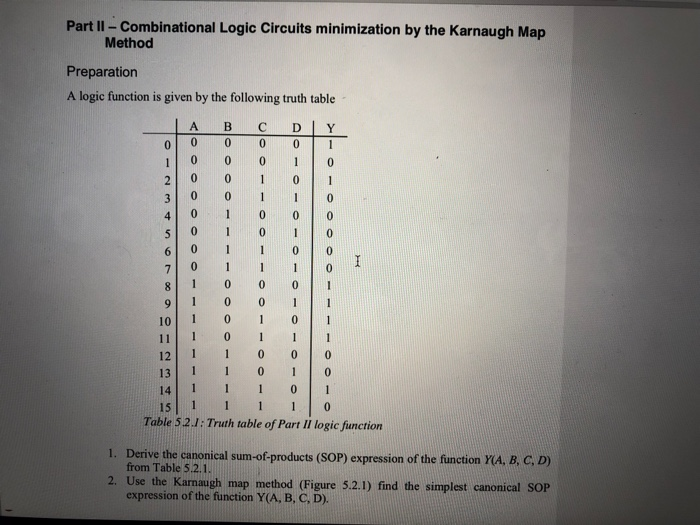

Question: Part II Combinational Logic Circuits minimization by the Karnaugh Map Method Preparation A logic function is given by the following truth table BCDY 10 1

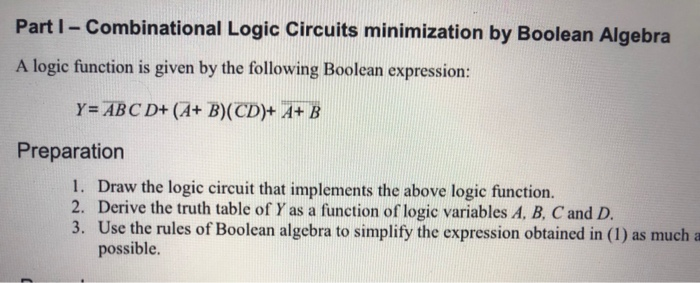

Part II Combinational Logic Circuits minimization by the Karnaugh Map Method Preparation A logic function is given by the following truth table BCDY 10 1 0 0 1 11 0 1 12 1 1 0 00 13 1 1 0 0 14 1 1 1 01 1s1 1 1 10 Table 5 21: Truth table of Part Illogic function 1. Derive the canonical sum-of products (sOP) . Derive the canonical sum-of-products (SOP) expression of the function Y(A, B, C, D) 2. Use the Karnaugh map method (Figure 5.2.1) find the simplest canonical SOP from Table 5.2.1 expression of the function Y(A, B, C. D). Part I - Combinational Logic Circuits minimization by Boolean Algebra A logic function is given by the following Boolean expression: Y ABCD+ (A+ B)(CD)+ A+B Preparation 1. Draw the logic circuit that implements the above logic function. 2. Derive the truth table of Y as a function of logic variables A, B, C and D. 3. Use the rules of Boolean algebra to simplify the expression obtained in (1) as much a possible

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts