Question: Please answer both a and b completely and explain your answers. Thank you! For question 3, refer to the pipeline design with forwarding and (load-use)

Please answer both a and b completely and explain your answers. Thank you!

Please answer both a and b completely and explain your answers. Thank you!

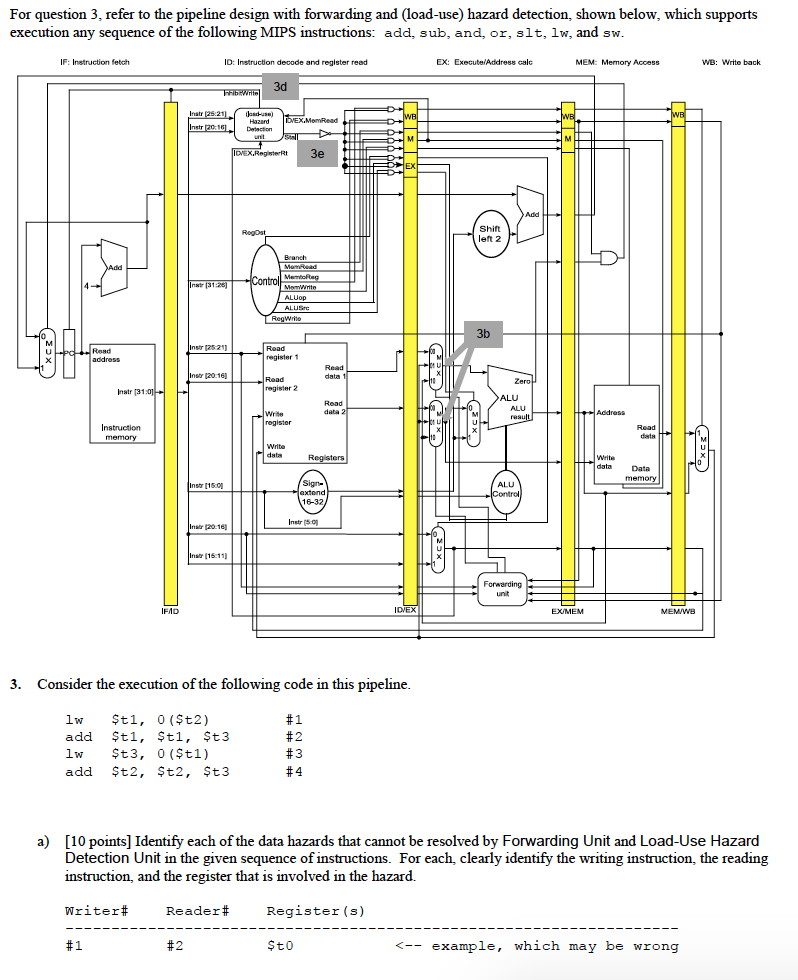

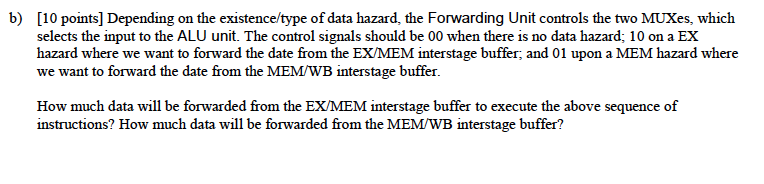

For question 3, refer to the pipeline design with forwarding and (load-use) hazard detection, shown below, which supports execution any sequence of the following MIPS instructions: add, sub, and, or, slt, 1w, and sw IF: Instruction fetch ID: Instruction decode and register read MEM: Memory Access WB: Write back 3d VEX.Register 3e Shift left 2 ALUop 3b 25211 Ul register 1 (2016) register 2 Instr [31 ALU Write dataData 15.00 Instr (50 20 16 IFAD IDVEX 3. Consider the execution of the following code in this pipeline lw $tl, 0 ($t2) add tl, t1, $t3 lw $t3, 0 ($tl) add $t2, $t2, t3 #1 #2 #3 #4 a) [10 points] Identify each of the data hazards that cannot be resolved by Forwarding Unit and Load-Use Hazard Detection Unit in the given sequence of instructions. For each, clearly identify the writing instruction, the reading instruction, and the register that is involved in the hazard. Writer# Reader# Register (s) #1 #2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts