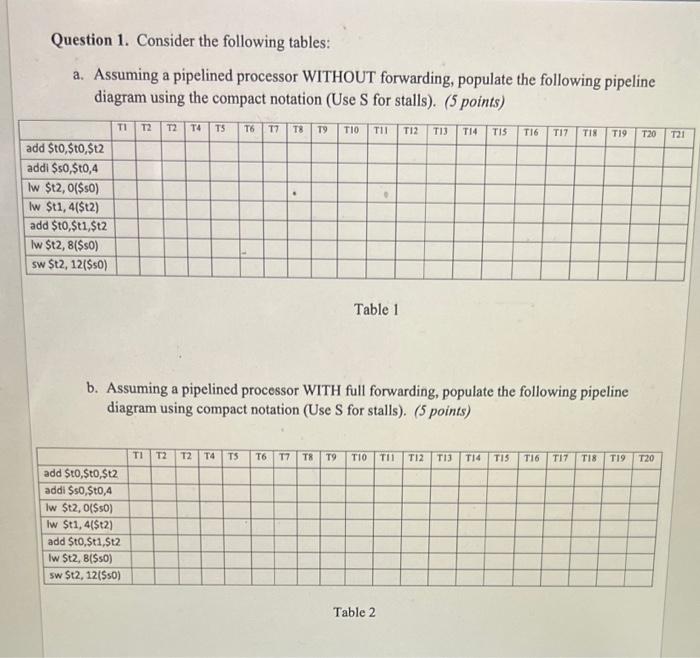

Question: Question 1. Consider the following tables: a. Assuming a pipelined processor WITHOUT forwarding, populate the following pipeline diagram using the compact notation (Use S

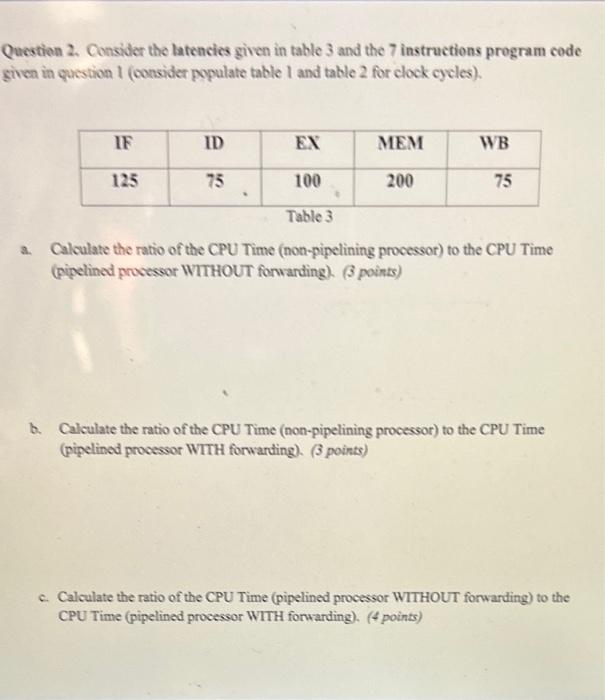

Question 1. Consider the following tables: a. Assuming a pipelined processor WITHOUT forwarding, populate the following pipeline diagram using the compact notation (Use S for stalls). (5 points) TI T2 T2 T4 TS T6 17 T8 19 T10 TII T12 T13 T14: T15 T16 T17 718 T19 T20 721 add $to,$to,$12 addi $50,$t0,4 lw $12,0($50) lw $t1, 4($12) add $10,$t1,$12 Iw $12, 8($50) sw St2, 12($50) . Table 1 b. Assuming a pipelined processor WITH full forwarding, populate the following pipeline diagram using compact notation (Use S for stalls). (5 points) TI T2 T2 T4 T5 T6 T7 T8 T9 T10 add $to,$to,$t2 addi $50,$t0,4 lw $12,0($50) Iw St1, 4($12) add St0,$t1,St2 Iw St2, 8($50) sw $12, 12($50) Table 2 T12 T13 T14 TIS T16 T17 T18 T19 T20 Question 2. Consider the latencies given in table 3 and the 7 instructions program code given in question 1 (consider populate table 1 and table 2 for clock cycles). IF ID EX MEM WB 125 75 100 200 75 Table 3 a. Calculate the ratio of the CPU Time (non-pipelining processor) to the CPU Time (pipelined processor WITHOUT forwarding). (3 points) b. Calculate the ratio of the CPU Time (non-pipelining processor) to the CPU Time (pipelined processor WITH forwarding). (3 points) c. Calculate the ratio of the CPU Time (pipelined processor WITHOUT forwarding) to the CPU Time (pipelined processor WITH forwarding). (4 points)

Step by Step Solution

There are 3 Steps involved in it

To solve the problem lets tackle it step by step Question 1 a Pipelined Processor WITHOUT Forwarding ... View full answer

Get step-by-step solutions from verified subject matter experts