Question: please don't copy other works for the question above do: 1. Structural Verilog implementations 2. Dataflow Verilog implementations 3. show that the outputs match through

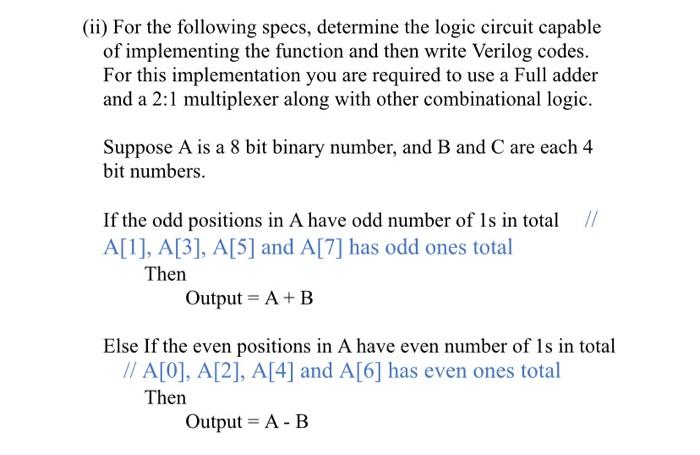

For each of the questions you are required to do both Structural and Dataflow Verilog implementations and show that the outputs match through waveforms. You can use either Xilinx ISE or the free online tools (ii) For the following specs, determine the logic circuit capable of implementing the function and then write Verilog codes. For this implementation you are required to use a Full adder and a 2:1 multiplexer along with other combinational logic. Suppose A is a 8 bit binary number, and B and C are each 4 bit numbers. If the odd positions in A have odd number of 1s in total A[1],A[3],A[5] and A[7] has odd ones total Then Output =A+B Else If the even positions in A have even number of 1s in total // A[0],A[2],A[4] and A[6] has even ones total Then Output = A B

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts