Question: Please help! This is to be done with verilog using the mobaXterm program 2. Last in First Out (LIFO) Write a module lifo.sv that implements

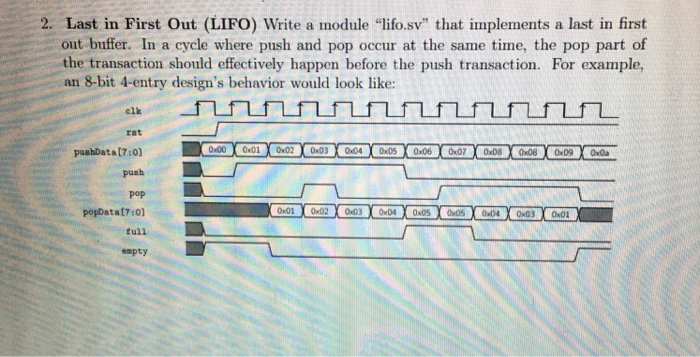

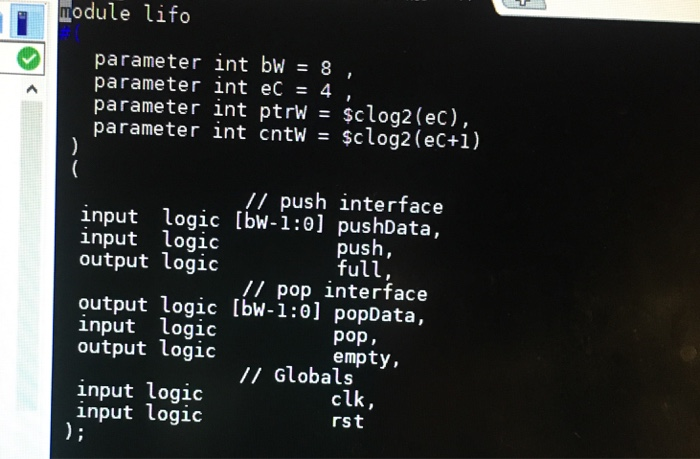

2. Last in First Out (LIFO) Write a module lifo.sv" that implements a last in first out buffer. In a cycle where push and pop occur at the same time, the pop part of the transaction should effectively happen before the push transaction. For example, an 8-bit 4-entry design's behavior would look like: clk rat pashDatat7:0)000 oa 0402 00 004 045 0:06 000 0.0 push POP popData[7:01 full eapty module lifo parameter int bw = 8 parameter int eC4 , parameter int ptrw sclog2(ec), parameter int cnth Sclog2 (eC+1) input Logic tbv.aush pusarftse input logic [bw-1:0] pushData, input logic output logic push, full, // pop interface output logic [bw-1:01 popData, input logic output logic pop, empty, // Globals input logic input logic clk, rst

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts