Question: please I need help on this homework in Advanced Comp Architectures or the microprogrammed architecture of Figure 1, give the sequence of actions required to

please I need help on this homework in Advanced Comp Architectures

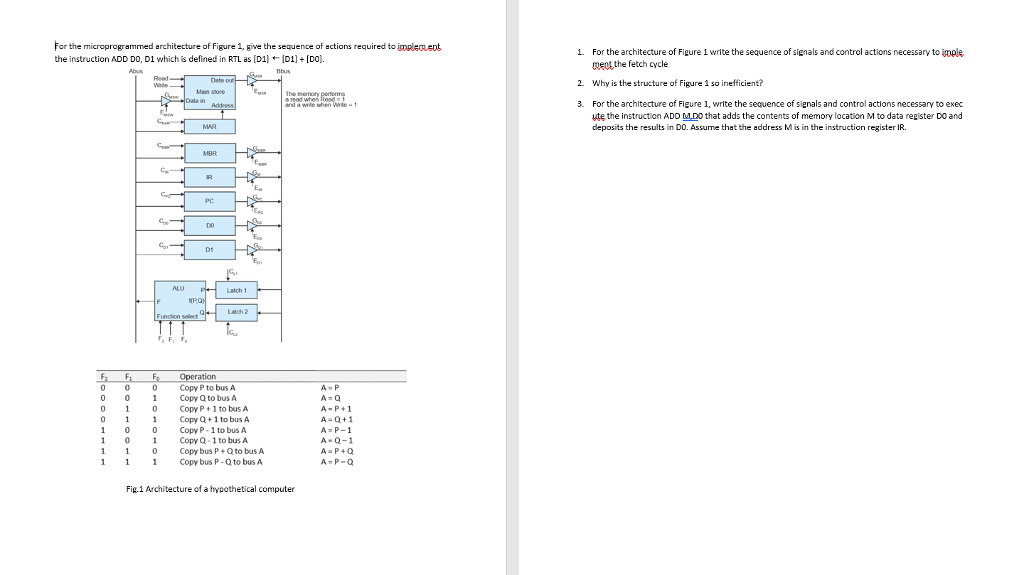

or the microprogrammed architecture of Figure 1, give the sequence of actions required to inplement the instruction ADD D0, D1 which is defined in RTL as [D1D[DO. 1 For the architecture of Figure 1 write the sequence of signals and control actions necessary to ipple ment the fetch cycle Why is the structure of Figure 1 so inefficient? 2. For the architecture of Figure 1, write the sequence of sienals and control actions necessary to exec ute the instruction ADD MDO that adds the contents of memory location M to data register DO and deposits the results in DO. Assume that the address Mis in the instructian register IR. 3. 0 0 0 0Copy P to bus A Ca to bus A 0 Copy P 1 to bus A 0 Copy Q+1 to bus A Copy P-1 to bus A 1 0CopyQ-1 to bus A A-P+1 A-Q+1 A P-1 A Q-1 0 1 1 0Cbus P+Qto bus A Copy bus P- Q to bus A 1 1 A-P-Q Fig.1 Architecture of a hypothetical computer

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts