Question: Please make sure the answer is correct. 234 CHAPTER6 CPU DESIGN 6.3.1 SpecificATiONS fOR A RElATivEly SimplE CPU Chapter 3 introduced the instruction set architecture

Please make sure the answer is correct.

Please make sure the answer is correct.

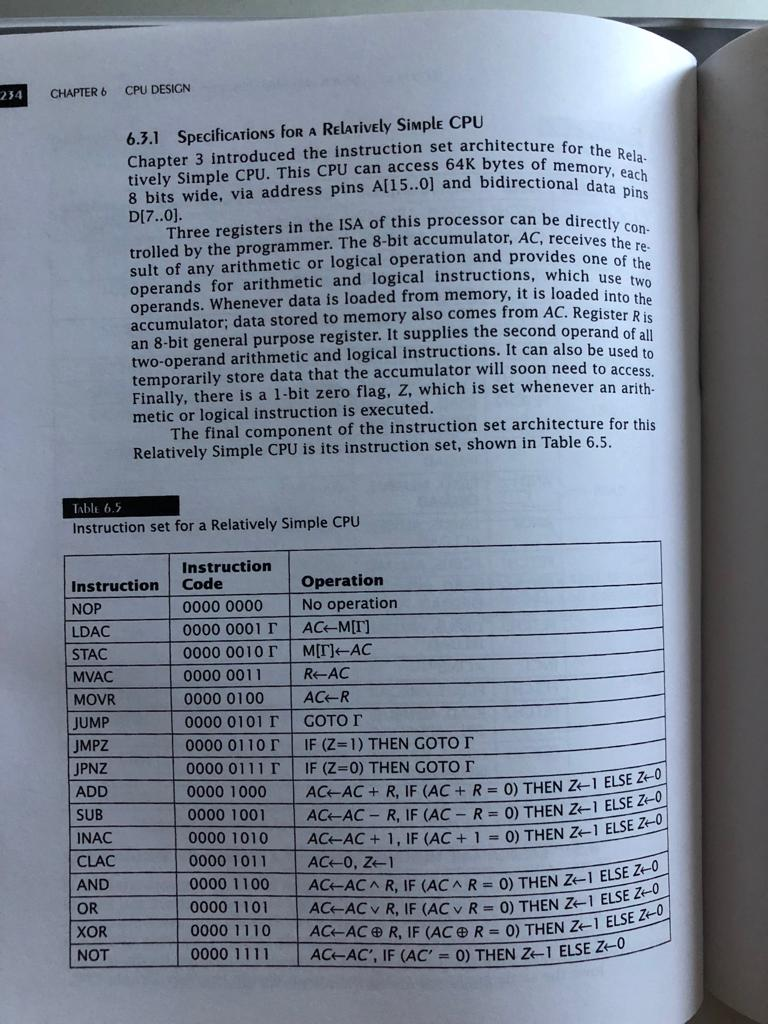

234 CHAPTER6 CPU DESIGN 6.3.1 SpecificATiONS fOR A RElATivEly SimplE CPU Chapter 3 introduced the instruction set architecture for tively Simple CPU. This CPU can access 64K bytes of memo 8 bits wide, via address pins Al15.0] and bidirectional data D[7..0] a pins Three registers in the ISA of this processor can be dir trolled by the programmer. The 8-bit accumulator, AC, rece sult of any arithmetic or logical operation and provides o operands for arithmetic and logical instructions, which operands. Whenever data is loaded from me accumulator; data stored to memory also comes from AC. Register an 8-bit general purpose register. It supplies the second oper two-operand arithmetic and logical instructions. It can also be us temporarily store data that the accumulator will soon need to acc Finally, there is a 1-bit zero flag, z, which is set whenever an a metic or logical instruction is executed. ves the re one of the use two mory, it is loaded into the Ris and of all ed to rith The final component of the instruction set architecture for this Relatively Simple CPU is its instruction set, shown in Table 6.5 lAblE 6.5 Instruction set for a Relatively Simple CPU Instruction Instruction Code NOP LDAC STAC MVAC MOVR JUMP JMPZ JPNZ ADD SUB INAC CLAC AND OR XOR NOT Operation No operation 0000 0001 AC-MIT] 0000 00 10 | MIT](-AC 0000 0011 0000 0100 ACR 0000 0101 | GOTO 0000 01 10 | IF (Z 1) THEN GOTO 0000 011 1 | IF (Z=0) THEN GOTO RE-AC AG-AC + R, IF (AC + R = 0) THEN Ze-l ELSEz-0 AG-AC R, IF (AC-R 0) THEN Z 1 ELSE Z- 1 ELSE Z-0 0000 1001 0000 1010 AC-AC+1, IF (AC +1 0) THEN 2 0000 1011 AC-0, Z-1 0000 1100 AG-ACA R, IF (ACAR=0) THENz-1. ELSEz- 0000 1101 AC-A 00001 1 10 | AG-ACRIF(ACOR-0) THEN 2- 0000 1 1 1 1 | AG-AC, IF (AC, 0)THENZ-1 ELSEz- CV R, IF (ACV R 0) THEN Z1 ELSE Z Z1 ELSE Z-0 234 CHAPTER6 CPU DESIGN 6.3.1 SpecificATiONS fOR A RElATivEly SimplE CPU Chapter 3 introduced the instruction set architecture for tively Simple CPU. This CPU can access 64K bytes of memo 8 bits wide, via address pins Al15.0] and bidirectional data D[7..0] a pins Three registers in the ISA of this processor can be dir trolled by the programmer. The 8-bit accumulator, AC, rece sult of any arithmetic or logical operation and provides o operands for arithmetic and logical instructions, which operands. Whenever data is loaded from me accumulator; data stored to memory also comes from AC. Register an 8-bit general purpose register. It supplies the second oper two-operand arithmetic and logical instructions. It can also be us temporarily store data that the accumulator will soon need to acc Finally, there is a 1-bit zero flag, z, which is set whenever an a metic or logical instruction is executed. ves the re one of the use two mory, it is loaded into the Ris and of all ed to rith The final component of the instruction set architecture for this Relatively Simple CPU is its instruction set, shown in Table 6.5 lAblE 6.5 Instruction set for a Relatively Simple CPU Instruction Instruction Code NOP LDAC STAC MVAC MOVR JUMP JMPZ JPNZ ADD SUB INAC CLAC AND OR XOR NOT Operation No operation 0000 0001 AC-MIT] 0000 00 10 | MIT](-AC 0000 0011 0000 0100 ACR 0000 0101 | GOTO 0000 01 10 | IF (Z 1) THEN GOTO 0000 011 1 | IF (Z=0) THEN GOTO RE-AC AG-AC + R, IF (AC + R = 0) THEN Ze-l ELSEz-0 AG-AC R, IF (AC-R 0) THEN Z 1 ELSE Z- 1 ELSE Z-0 0000 1001 0000 1010 AC-AC+1, IF (AC +1 0) THEN 2 0000 1011 AC-0, Z-1 0000 1100 AG-ACA R, IF (ACAR=0) THENz-1. ELSEz- 0000 1101 AC-A 00001 1 10 | AG-ACRIF(ACOR-0) THEN 2- 0000 1 1 1 1 | AG-AC, IF (AC, 0)THENZ-1 ELSEz- CV R, IF (ACV R 0) THEN Z1 ELSE Z Z1 ELSE Z-0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts