Question: please solve with details Safe Deposit Box Learning Objectives To model, simulate and synthesize digital circuits using Verilog HDL models and/or schematic diagrams to solve

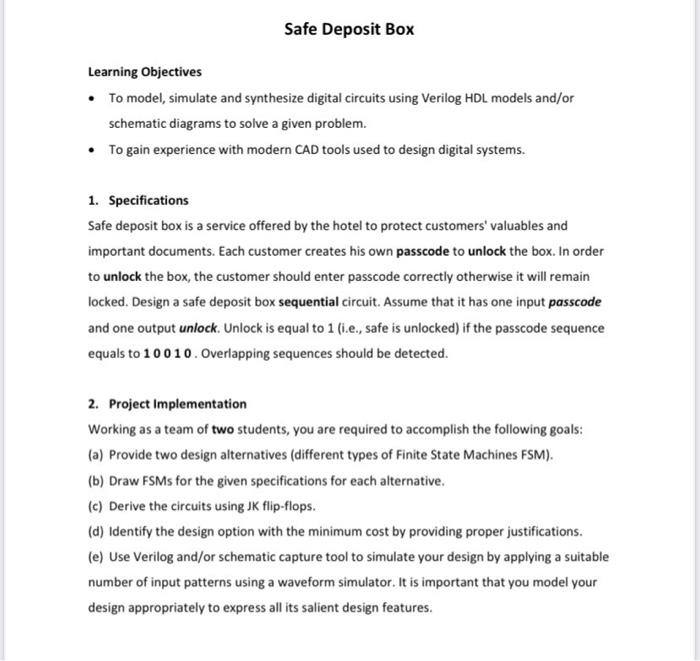

Safe Deposit Box Learning Objectives To model, simulate and synthesize digital circuits using Verilog HDL models and/or schematic diagrams to solve a given problem. To gain experience with modern CAD tools used to design digital systems. 1. Specifications Safe deposit box is a service offered by the hotel to protect customers' valuables and important documents. Each customer creates his own passcode to unlock the box. In order to unlock the box, the customer should enter passcode correctly otherwise it will remain locked. Design a safe deposit box sequential circuit. Assume that it has one input passcode and one output unlock. Unlock is equal to 1 (i.e., safe is unlocked) if the passcode sequence equals to 10010. Overlapping sequences should be detected. 2. Project Implementation Working as a team of two students, you are required to accomplish the following goals: (a) Provide two design alternatives (different types of Finite State Machines FSM). (b) Draw FSMs for the given specifications for each alternative. (c) Derive the circuits using JK flip-flops. (d) Identify the design option with the minimum cost by providing proper justifications. (e) Use Verilog and/or schematic capture tool to simulate your design by applying a suitable number of input patterns using a waveform simulator. It is important that you model your design appropriately to express all its salient design features

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts