Question: Please write program in VHDL! Objective The objective of this laboratory is to introduce simple sequential circuit design by creating a fundamental circuit design element,

Please write program in VHDL!

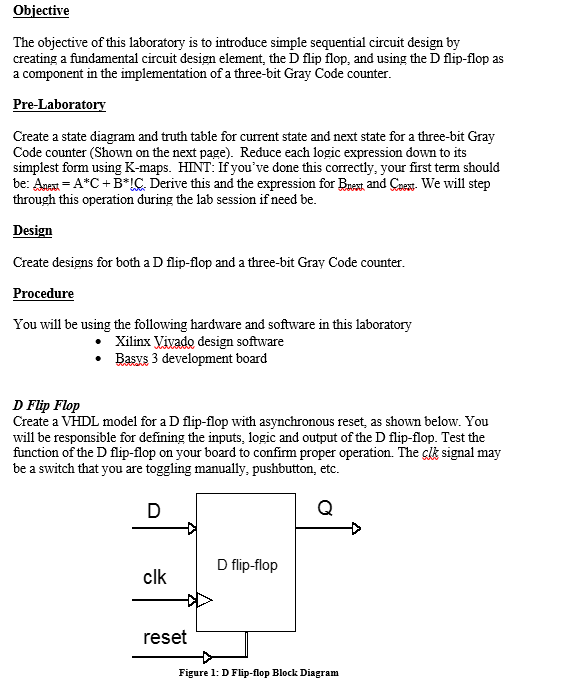

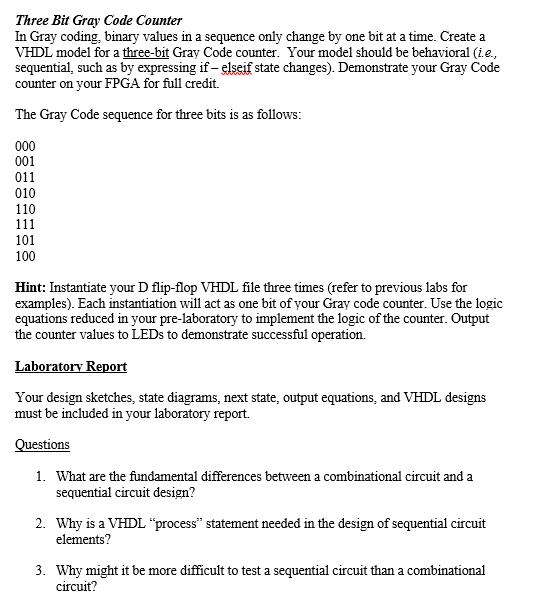

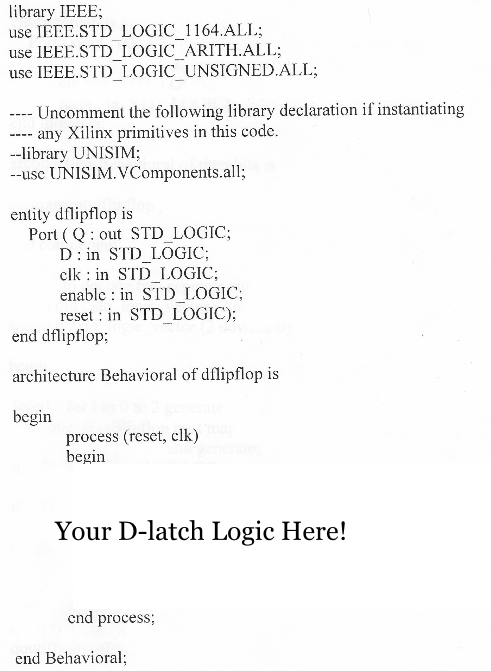

Objective The objective of this laboratory is to introduce simple sequential circuit design by creating a fundamental circuit design element, the D flip flop, and using the D flip-flop as a component in the implementation of a three-bit Gray Code counter. Pre-Laborato Create a state diagram and truth table for current state and next state for a three-bit Grajy Code counter (Shown on the next page). Reduce each logic expression down to its simplest form using K-maps. HINT: Ifyou've done this correctly, your first term should be: Ane-A*CB C. Derive this and the expression for Buex and Coex. We will step through this operation during the lab session if need be Design Create designs for both a D flip-flop and a three-bit Gray Code counter Procedure You will be using the following hardware and software in this laboratory Xilinx Vivado design software .Basys 3 development board D Flip Flop Create a VHDL model for a D flip-flop with asynchronous reset, as shown below. You will be responsible for defining the inputs, logic and output of the D flip-flop. Test the function of the D flip-flop on your board to confirm proper operation. The clk signal may be a switch that you are toggling manually, pushbutton, etc. D flip-flop clk reset Figure 1: D Flip-flop Block Diagram Objective The objective of this laboratory is to introduce simple sequential circuit design by creating a fundamental circuit design element, the D flip flop, and using the D flip-flop as a component in the implementation of a three-bit Gray Code counter. Pre-Laborato Create a state diagram and truth table for current state and next state for a three-bit Grajy Code counter (Shown on the next page). Reduce each logic expression down to its simplest form using K-maps. HINT: Ifyou've done this correctly, your first term should be: Ane-A*CB C. Derive this and the expression for Buex and Coex. We will step through this operation during the lab session if need be Design Create designs for both a D flip-flop and a three-bit Gray Code counter Procedure You will be using the following hardware and software in this laboratory Xilinx Vivado design software .Basys 3 development board D Flip Flop Create a VHDL model for a D flip-flop with asynchronous reset, as shown below. You will be responsible for defining the inputs, logic and output of the D flip-flop. Test the function of the D flip-flop on your board to confirm proper operation. The clk signal may be a switch that you are toggling manually, pushbutton, etc. D flip-flop clk reset Figure 1: D Flip-flop Block Diagram

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts