Question: problem 1 Lab Activities 4 and 5 Assigned: November 9, 2017 Due Date: November 20, 2017 Objectives of the lab activity . Learn how to

problem 1

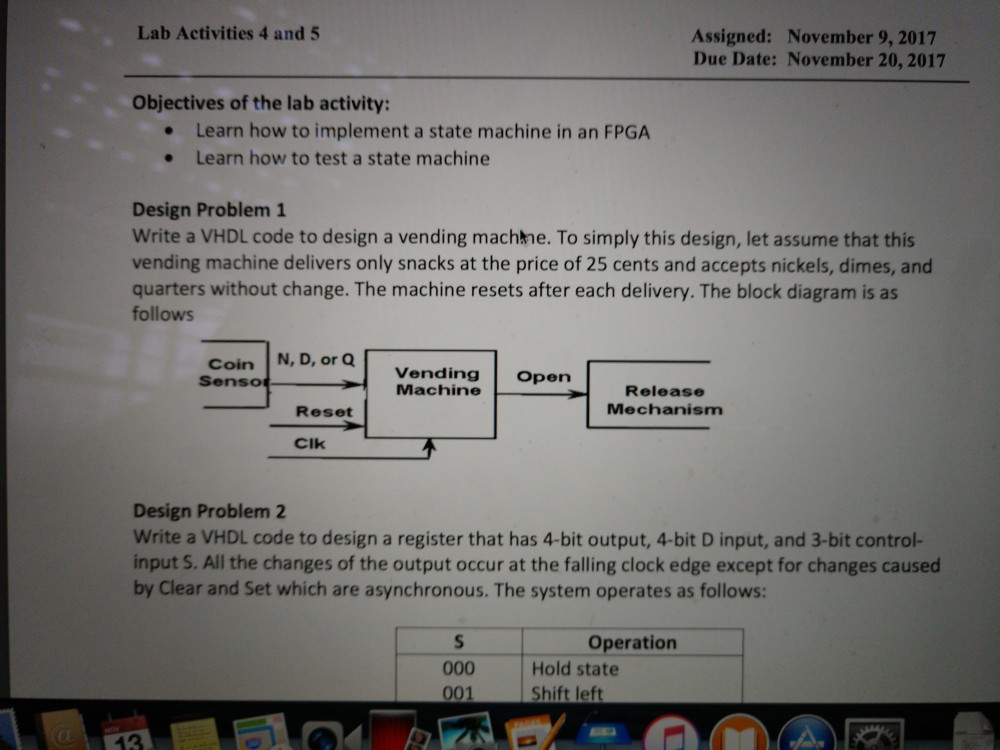

Lab Activities 4 and 5 Assigned: November 9, 2017 Due Date: November 20, 2017 Objectives of the lab activity . Learn how to implement a state machine in an FPGA . Learn how to test a state machine Design Problem 1 Write a VHDL code to design a vending machthe. To simply this design, let assume that this vending machine delivers only snacks at the price of 25 cents and accepts nickels, dimes, and quarters without change. The machine resets after each delivery. The block diagram is as follows Coin N, D, or Q SensoMachine Vending Open Release Mechanism - Reset Clk Design Problem 2 Write a VHDL code to design a register that has 4-bit output, 4-bit D input, and 3-bit control- input S. All the changes of the output occur at the falling clock edge except for changes caused by Clear and Set which are asynchronous. The system operates as follows: Operation Hold state Shift left 001

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts