Question: Problem 1 : You are provided with three SystemVerilog files that implement the FIFO buffer shown below: fifo.sv , fifo _ ctrl . sv ,

Problem :

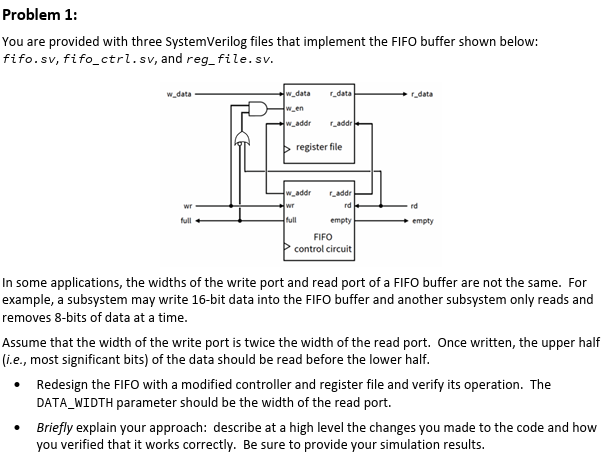

You are provided with three SystemVerilog files that implement the FIFO buffer shown below:

fifo.sv fifoctrlsv and regfile.sv

In some applications, the widths of the write port and read port of a FIFO buffer are not the same. For

example, a subsystem may write bit data into the FIFO buffer and another subsystem only reads and

removes bits of data at a time.

Assume that the width of the write port is twice the width of the read port. Once written, the upper half

ie most significant bits of the data should be read before the lower half.

Redesign the FIFO with a modified controller and register file and verify its operation. The

DATAWIDTH parameter should be the width of the read port.

Briefly explain your approach: describe at a high level the changes you made to the code and how

you verified that it works correctly. Be sure to provide your simulation results.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock