Question: Problem #2 125 pts] Consider the internal structure of the pseudo-CPU discussed in class augmented with a single-port register file i.e., only one register value

![Problem #2 125 pts] Consider the internal structure of the pseudo-CPU](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f539b918b30_12866f539b8898bc.jpg)

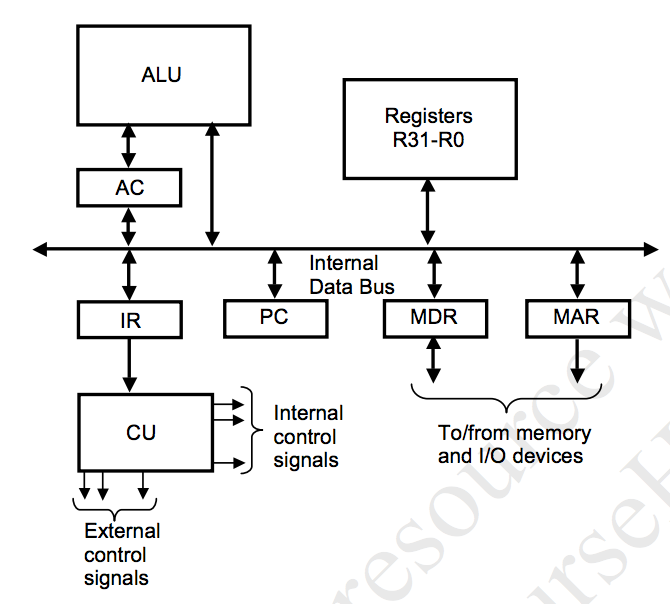

Problem #2 125 pts] Consider the internal structure of the pseudo-CPU discussed in class augmented with a single-port register file i.e., only one register value can be read at a time) containing 32 8-bit registers (RO-R31). Suppose the pseudo-CPU can be used to implement the AVR instruction ST -x, R3. Give the sequence of microoperations required to Fetch and Execute AVR's ST -x, R3 instruction. Your solutions should result in exactly 6 cycles for the fetch cycle and 7 cycles for the execute cycle. You may assume only the AC and PC registers have the capability to increment/decrement itself. Assume MDR register is 8-bit wide (which implies that memory is organized into consecutive addressable bytes), and AC, PC, IR, and MAR are 16-bit wide. Also, assume Internal Data Bus is 16-bit wide and thus can handle 8-bit or 16-bit (as well as portion of 8-bit or 16-bit transfers in one microoperation. Clearly state any other assumptions made

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts