Question: Problem 2 . A . Design the simplest dynamic CMOS logic gate that implements the function Y ? b = a r ( A *

Problem

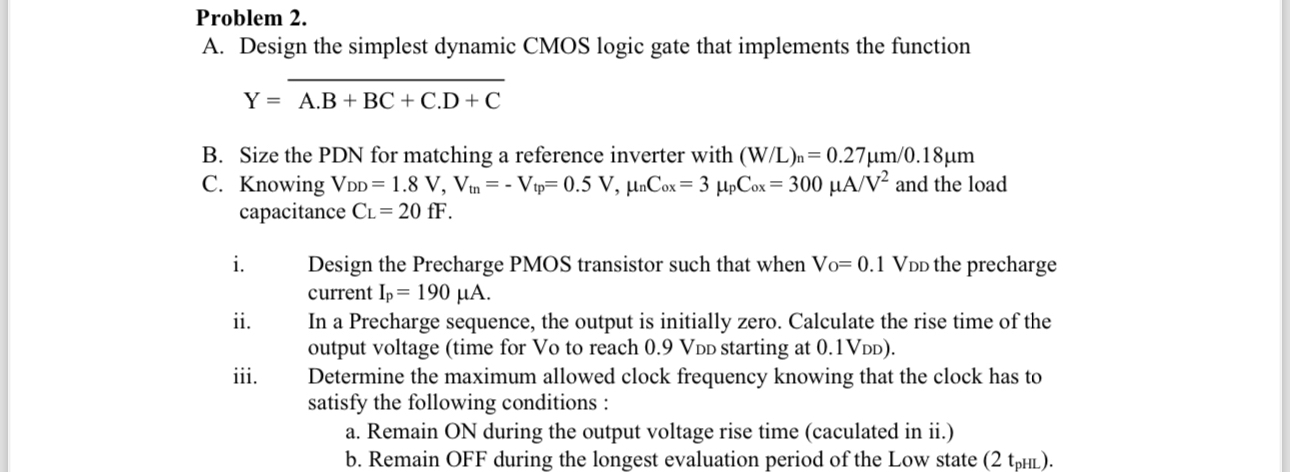

A Design the simplest dynamic CMOS logic gate that implements the function

B Size the PDN for matching a reference inverter with

C Knowing and the load capacitance

i Design the Precharge PMOS transistor such that when VDD the precharge current

ii In a Precharge sequence, the output is initially zero. Calculate the rise time of the output voltage time for Vo to reach VDD starting at VDD

iii. Determine the maximum allowed clock frequency knowing that the clock has to satisfy the following conditions :

a Remain ON during the output voltage rise time caculated in ii

b Remain OFF during the longest evaluation period of the Low state :

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock